### Njulla and GreenLab: Programming Mote-Class Devices in the Context of a Testbed Designed for the Energy Harvesting Regime

Aslak Johansen aslj@itu.dk

PhD Dissertation

IT University of Copenhagen

Advisor: Philippe Bonnet phbo@itu.dk

March 14, 2014

#### Abstract

This dissertation is the conclusion of joint work between the IT University of Copenhagen (ITU) and DELTA, a danish advanced technology institute, in the context of DELTA's strategic action on services in wireless sensor networks (WSN) for long-term environmental monitoring.

Wireless sensor networks are composed of mote class devices: small computers with severely limited resources in terms of memory size, processing speed, storage size, wireless communication throughput, and power budget. In most application contexts, mote class devices are powered from batteries or even wall socket. However, for long term environmental monitoring, it is necessary to source their power from energy harvesters. In order to allow DELTA customers to experiment with applications adapted to the energy harvesting regime, I designed and implemented the GreenLab testbed.

I found TinyOS – the dominant framework for mote programming in the last decade – to be a bad fit for implementing such a testing facility. I revisited the design choices and found several issues – mainly regarding component system, arbitration and hardware abstractions – that hinders the ease of debugging as well as the applicability of the framework. During its evolution, TinyOS has built a component system so dense that the application programmers rarely grasp the implications of their choices, yet those implications often propagate across component boundaries.

As an alternative, I present Njulla, a mote programming framework designed with ease of debugging as the primary design principle. I take the opportunity to reflect on the ease of debugging, and what it means to the mote programmer.

#### Acknowledgments

The last three years have been a great experience. DELTA has kept revealing new facets to their gamut of expertise. At ITU I have gotten a new insight into the educational system and started developing theories about it. Both have provided me with new friends.

My advisor – Philippe Bonnet – allowed me to follow my own paths, nudging me back on track each time I had followed a tangent too far. Somehow he always managed to know what to tell me. Often the feedback would seem immediately obvious once received. It would be delivered in a way that made me understand the underlying reasoning. I could gain an understanding. During my time at ITU I have supervised several groups of master-level students. Being a student of Philippe's has made me a better advisor for them, and for myself. I am immensely grateful for this.

Thanks to Dušan Vučković for many good conversations and taking the time to elevate my understanding of electronics to a usable level.

Jesper Schaumburg-Müller – my father – has played a pivotal role in these years. He would often help me make sense of all my new experiences.

Also thanks to Geoffrey Challen for advising me during my stay abroad. He, Suzanna and Choo-Choo hosted me during the first part of this stay and proved to be excellent company.

The remainder of the list is long and complex. My family and friends all did their parts in less direct (but often equally constructive) ways. I am amazed at the magnitude of offered support and interest. It was appreciated.

# Contents

### List of Figures

| 1 | Intr                                                                        | oduction                                      | 12                         |

|---|-----------------------------------------------------------------------------|-----------------------------------------------|----------------------------|

|   | 1.1                                                                         | Thesis Context                                | 12                         |

|   | 1.2                                                                         | Data Acquisition Infrastructure               | 13                         |

|   | 1.3                                                                         | Problem                                       | 14                         |

|   | 1.4                                                                         | Approach                                      | 16                         |

|   | 1.5                                                                         | Contribution                                  | 17                         |

|   | 1.6                                                                         | Thesis Structure                              | 18                         |

| Ι | Sta                                                                         | te of the Art                                 | 20                         |

| 2 | Ene                                                                         | rgy Harvesting                                | 21                         |

| 2 | <b>Ene</b><br>2.1                                                           | ergy Harvesting                               | <b>21</b><br>22            |

| 2 |                                                                             |                                               |                            |

| 2 | 2.1                                                                         | Harvester                                     | 22                         |

| 2 | 2.1<br>2.2                                                                  | Harvester      Rectifier                      | 22<br>23                   |

| 2 | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul>                               | Harvester      Rectifier      Voltage Scaling | 22<br>23<br>23             |

| 2 | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol> | Harvester                                     | 22<br>23<br>23<br>23<br>23 |

9

|   | 3.2 | The Analog in Digital 20 |            |                      |      |  |

|---|-----|--------------------------|------------|----------------------|------|--|

|   | 3.3 | Mote                     | Channels   |                      | . 27 |  |

|   | 3.4 | AD Co                    | onversion  |                      | . 29 |  |

|   | 3.5 | Serial                   | Communi    | cation               | . 30 |  |

|   |     | 3.5.1                    | UART .     |                      | . 31 |  |

|   |     | 3.5.2                    | SPI        |                      | . 32 |  |

|   |     | 3.5.3                    | $I^2C$     |                      | . 32 |  |

|   | 3.6 | Periph                   | erals      |                      | . 34 |  |

|   | 3.7 | Case S                   | Study: Tel | osB                  | . 34 |  |

| 4 | Mot | e Prog                   | grammin    | g                    | 36   |  |

|   | 4.1 | Abstra                   | actions    |                      | . 36 |  |

|   |     | 4.1.1                    | Commun     | lication             | . 36 |  |

|   |     |                          | 4.1.1.1    | Serial communication | . 37 |  |

|   |     |                          | 4.1.1.2    | Radio                | . 37 |  |

|   |     |                          | 4.1.1.3    | Multiple Streams     | . 38 |  |

|   |     | 4.1.2                    | Interpret  | er                   | . 38 |  |

|   |     |                          | 4.1.2.1    | Interrupts           | . 38 |  |

|   |     |                          | 4.1.2.2    | Multiple Flows       | . 39 |  |

|   |     |                          | 4.1.2.3    | Arbitration          | . 40 |  |

|   |     | 4.1.3                    | Memory     |                      | . 41 |  |

|   | 4.2 | Power                    |            |                      | . 42 |  |

|   | 4.3 | Debug                    | ging       |                      | . 42 |  |

|   | 4.4 | TinyO                    | S          |                      | . 44 |  |

|   |     | 4.4.1                    | Program    | ming Model           | . 44 |  |

|   |     | 4.4.2                    | Hardwar    | e Abstraction        | . 45 |  |

|   |     | 4.4.3                    | Executio   | n Model              | . 46 |  |

|    |     |         | 4.4.3.1 Virtual Machines                                    | 46        |

|----|-----|---------|-------------------------------------------------------------|-----------|

|    |     | 4.4.4   | Resource Allocation                                         | 47        |

|    | 4.5 | Contil  | xi                                                          | 47        |

|    |     | 4.5.1   | Execution Model                                             | 48        |

|    |     | 4.5.2   | Reprogramming                                               | 48        |

|    |     | 4.5.3   | Preemptive Multitasking as a Library                        | 48        |

|    |     | 4.5.4   | Portability and Abstractions                                | 48        |

| 5  | Sen | sor Ne  | etwork Testbeds                                             | 50        |

|    | 5.1 | Existi  | ng Testbeds                                                 | 51        |

|    | 5.2 | Repro   | gramming                                                    | 52        |

|    |     | 5.2.1   | Unit of reprogramming                                       | 52        |

|    |     | 5.2.2   | Time of reprogramming                                       | 53        |

|    |     | 5.2.3   | Resident Component                                          | 54        |

| 6  | Deb | ougging | g a Mote Program                                            | 55        |

|    | 6.1 | Simula  | ation                                                       | 55        |

|    | 6.2 | Source  | e Debugging Systems                                         | 56        |

|    | 6.3 | Deploy  | yment Debugging                                             | 56        |

| 7  | Sun | nmary   |                                                             | 58        |

| II | C   | ontrib  | ution                                                       | 61        |

| 8  | Tin | yOS C   | ritique                                                     | 63        |

|    | 8.1 | The Il  | lusion of Hardware Independence                             | 64        |

|    |     | 8.1.1   | Interdependencies between Hardware and Programming Framwork | ne-<br>65 |

|    |     | 8.1.2   | Analysis of the TinyOS code base                            | 67        |

|   | 8.2 | Comp   | onents Considered Harmful       | 72 |

|---|-----|--------|---------------------------------|----|

|   |     | 8.2.1  | Understanding TinyOS Components | 72 |

|   |     | 8.2.2  | Porting TinyOS Components       | 72 |

|   |     | 8.2.3  | Debugging TinyOS Components     | 73 |

|   | 8.3 | Summ   | nary                            | 73 |

| 9 | Nju | lla    |                                 | 74 |

|   | 9.1 | Green  | Mote4                           | 74 |

|   | 9.2 | Design | n Space                         | 75 |

|   | 9.3 | Progra | amming Framework                | 76 |

|   |     | 9.3.1  | Build System                    | 76 |

|   |     | 9.3.2  | Memory Management               | 77 |

|   |     | 9.3.3  | Object (state) System           | 78 |

|   |     | 9.3.4  | Execution Model                 | 78 |

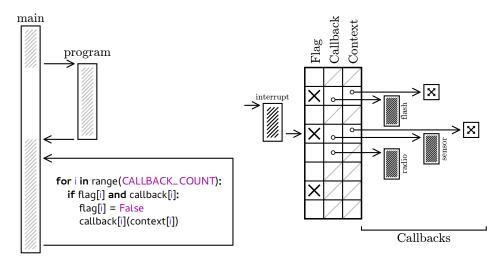

|   |     |        | 9.3.4.1 Callback System         | 79 |

|   |     |        | 9.3.4.2 Interrupt Processing    | 80 |

|   |     |        | 9.3.4.3 Programming Model       | 81 |

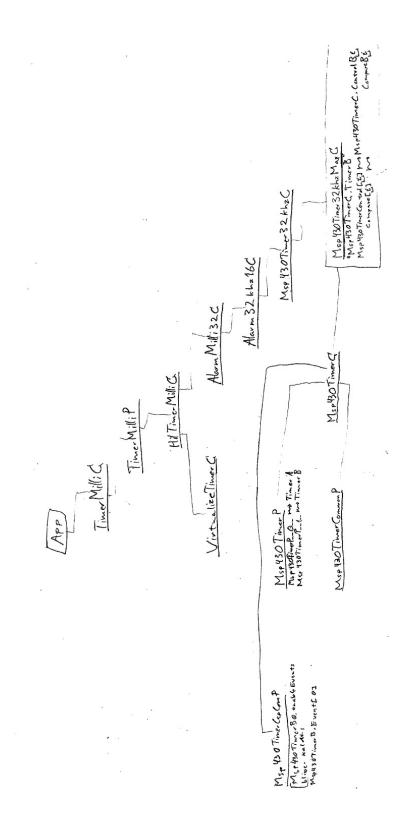

|   |     | 9.3.5  | Timers                          | 82 |

|   |     | 9.3.6  | ADC                             | 82 |

|   |     | 9.3.7  | Reprogramming                   | 82 |

|   |     |        | 9.3.7.1 Compiler limitations    | 84 |

|   |     |        | 9.3.7.2 Time of Reprogramming   | 86 |

|   |     |        | 9.3.7.3 Approach                | 86 |

|   |     | 9.3.8  | Implementation                  | 86 |

|   | 9.4 | Evalua | ation                           | 87 |

|   |     | 9.4.1  | Complexity                      | 87 |

|   |     | 9.4.2  | Portability                     | 88 |

|        | 9.4.3   | Ease of I | Debugging                | 89  |

|--------|---------|-----------|--------------------------|-----|

|        | 9.4.4   | Bar of E  | Cntry                    | 90  |

|        | 9.4.5   | Performa  | ance                     | 91  |

|        |         | 9.4.5.1   | Boot Time                | 91  |

|        |         | 9.4.5.2   | Boot Sequence            | 92  |

|        |         | 9.4.5.3   | Waking from Sleep        | 94  |

|        |         | 9.4.5.4   | Toggling of a Pin        | 96  |

|        |         | 9.4.5.5   | Serial Communication     | 98  |

|        | 9.4.6   | Conclusi  | ions                     | 100 |

| 9.5    | Discus  | sion and  | Future Work              | 101 |

| 10 Gre | enlah ' | Testbed   |                          | 104 |

|        |         |           |                          |     |

| 10.1   | Experi  | ment For  | m                        | 104 |

| 10.2   | Mote I  | Lifecycle |                          | 105 |

|        | 10.2.1  | Service S | State                    | 106 |

|        | 10.2.2  | Routing   |                          | 107 |

|        | 10.2.3  | Comman    | nd Instruction Set       | 108 |

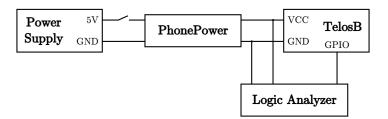

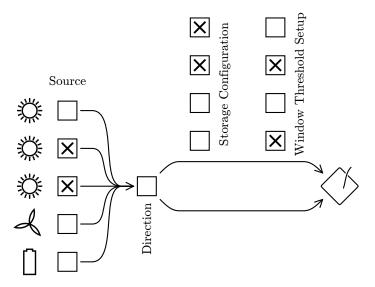

| 10.3   | Power   | Subsyste  | m                        | 110 |

|        | 10.3.1  | Configur  | ration                   | 110 |

|        | 10.3.2  | Interface | 9                        | 111 |

| 10.4   | Evalua  | tion      |                          | 111 |

|        | 10.4.1  | Testbed   | Experiments              | 112 |

|        | 10.4.2  | Input-va  | ried Distribution Plots  | 112 |

|        | 10.4.3  | Upload o  | of Program Image         | 113 |

|        | 10.4.4  | Reprogra  | amming                   | 114 |

|        | 10.4.5  | Downloa   | ad of Experiment Results | 116 |

|        | 10.4.6  | Conclusi  | ions                     | 117 |

| 10.5 Discussion and Future Work                               | . 119 |

|---------------------------------------------------------------|-------|

| 11 Debugging a Mote Program                                   | 121   |

| 11.1 Tools                                                    | . 121 |

| 11.1.1 Static Analysis                                        | . 121 |

| 11.1.2 Serial                                                 | . 122 |

| 11.1.3 Logging to RAM                                         | . 122 |

| 11.1.4 Leds                                                   | . 122 |

| 11.1.5 Logic Analyzer                                         | . 123 |

| 11.1.6 Decomposition                                          | . 123 |

| 11.1.7 Simulation                                             | . 124 |

| 11.1.8 JTAG Debugger                                          | . 124 |

| 11.2 Low-level Debugging Example                              | . 125 |

| 11.2.1 System                                                 | . 125 |

| 11.2.2 Process                                                | . 125 |

| 11.3 High-level Debugging Example                             | . 126 |

| 11.3.1 System                                                 | . 127 |

| 11.3.2 Diagnostics                                            | . 127 |

| 11.4 Methodology                                              | . 128 |

| 11.4.1 Design Principles                                      | . 128 |

| 11.4.2 Approach                                               | . 128 |

| 11.4.2.1 Adding Functionality                                 | . 129 |

| 11.4.2.2 When something goes Wrong $\ldots$ $\ldots$ $\ldots$ | . 129 |

| 12 Conclusion                                                 | 131   |

| Bibliography                                                  | 134   |

| Α | TinyOS | Timer | Abstraction |

|---|--------|-------|-------------|

|---|--------|-------|-------------|

| в | Pho | onePower Shield |     |  |  |  |  |

|---|-----|-----------------|-----|--|--|--|--|

|   | B.1 | Problem         | .47 |  |  |  |  |

|   | B.2 | Approach        | .47 |  |  |  |  |

|   | B.3 | Design          | .48 |  |  |  |  |

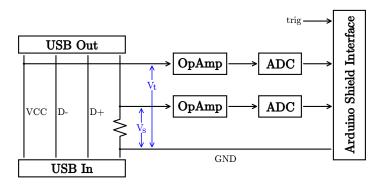

|   |     | B.3.1 Hardware  | .48 |  |  |  |  |

|   |     | B.3.2 Software  | .49 |  |  |  |  |

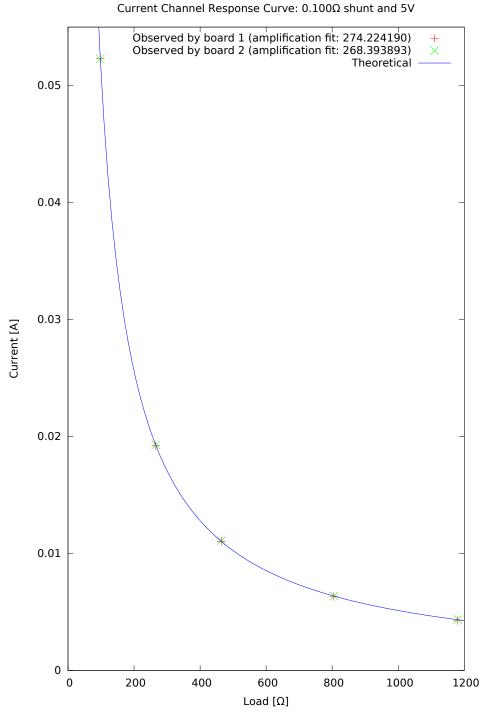

|   | B.4 | Calibration     | .51 |  |  |  |  |

# List of Figures

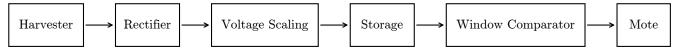

| 2.1 | The generic energy path of an energy harvesting node | 22 |

|-----|------------------------------------------------------|----|

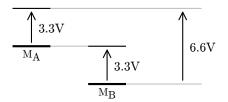

| 3.1 | Anchoring of ground planes                           | 27 |

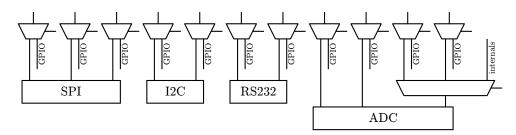

| 3.2 | Examples of pin to functional unit routing.          | 28 |

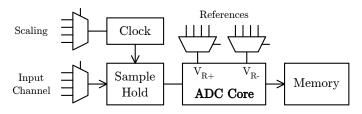

| 3.3 | Conceptual model of an ADC unit                      | 29 |

| 3.4 | UART frame format.                                   | 31 |

| 3.5 | SPI line transitions.                                | 33 |

| 3.6 | The TelosB channel dependency graph                  | 35 |

| 4.1 | Two-phase fragmented flow example                    | 40 |

| 4.2 | Threaded flow example.                               | 40 |

| 5.1 | Levels of instrumentation among mote testbeds        | 50 |

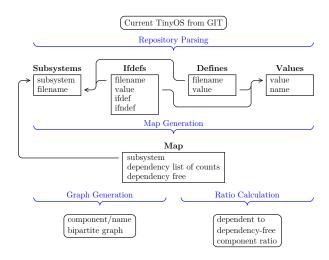

| 8.1 | Model for analyzing the TinyOS code base             | 68 |

| 8.2 | Number of platform define uses in subsystems         | 70 |

| 8.3 | Mapping of platform define uses to causes            | 71 |

| 9.1 | The GreenMote4 channel dependency graph              | 74 |

| 9.2 | Help message from build script                       | 77 |

| 9.3 | Njulla object definition example.                    | 79 |

| 9.4 | Njulla callback example                              | 80 |

| 9.5  | Overview of the Njulla execution model                                                                 | 80  |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 9.6  | Njulla example of a double-buffered UART echo client                                                   | 81  |

| 9.7  | Njulla example of a 3 bit led clock based on abstract timers                                           | 83  |

| 9.8  | Njulla example of using the ADC to implement a random generator.                                       | 84  |

| 9.9  | Njulla example jumping back and forth between two program images.                                      | 85  |

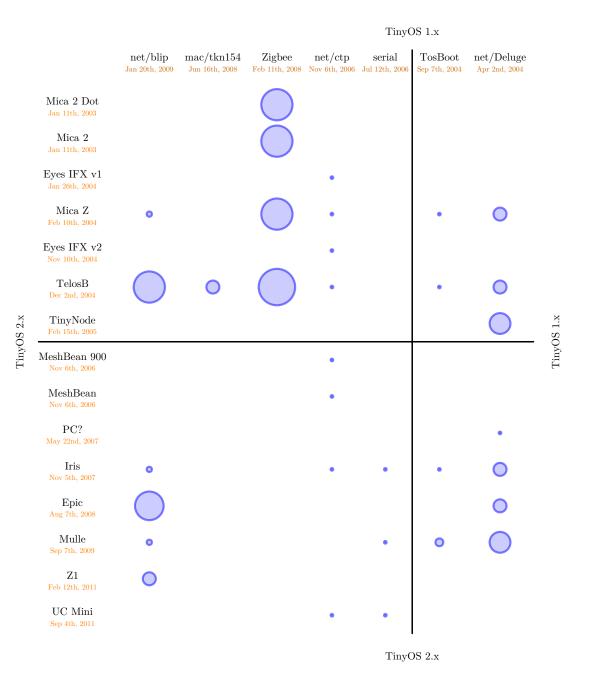

| 9.10 | Distribution of TinyOS code relating to the TelosB                                                     | 88  |

| 9.11 | Distribution of Njulla code relating to the TelosB                                                     | 88  |

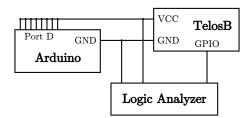

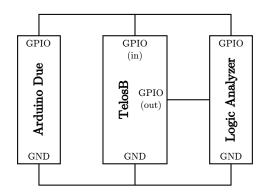

| 9.12 | Experimental setup for measuring boot time                                                             | 92  |

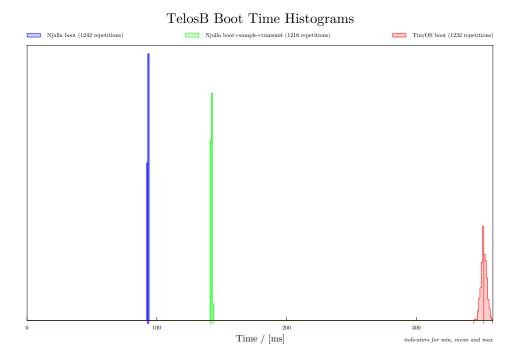

| 9.13 | Histograms of boot times.                                                                              | 93  |

| 9.14 | Values for boot times                                                                                  | 93  |

| 9.15 | Experimental setup for measuring the boot sequence                                                     | 94  |

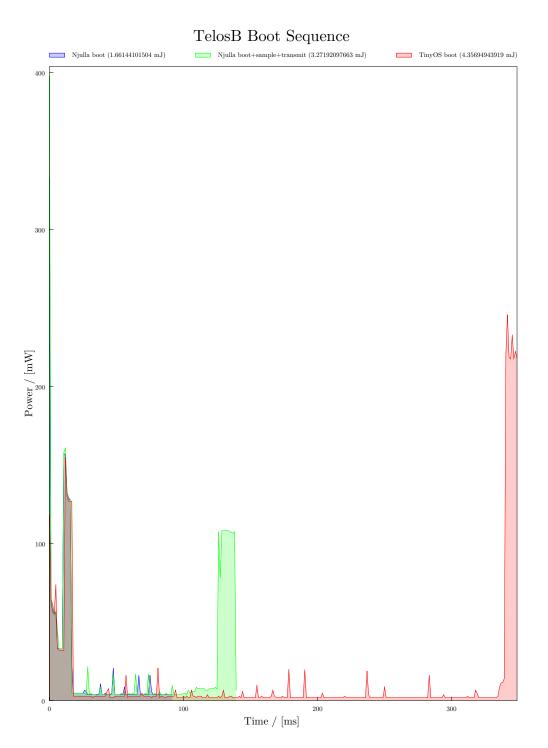

| 9.16 | Power draw during boot for Njulla and TinyOS on the TelosB                                             | 95  |

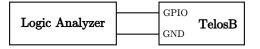

| 9.17 | Experimental setup for measuring the time it takes to wake up from sleep initiated by a pin transition | 96  |

| 9.18 | Reaction times to a pin transition following LPM4 sleep                                                | 97  |

| 9.19 | Experimental setup for measuring the time it takes to toggle a pin.                                    | 97  |

| 9.20 | Times for toggling of a pin.                                                                           | 98  |

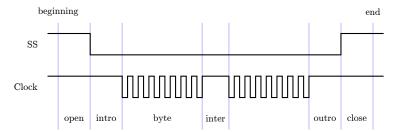

| 9.21 | Relevant metrics for SPI benchmarking                                                                  | 98  |

| 9.22 | Experimental setup for measuring the SPI communication                                                 | 99  |

| 9.23 | Times for the components of SPI transmission.                                                          | 100 |

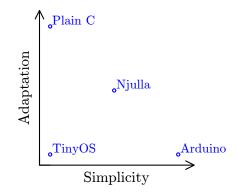

| 9.24 | The design space of simplicity and adaptation to the sub-sleep<br>energy harvesting regime.            | 101 |

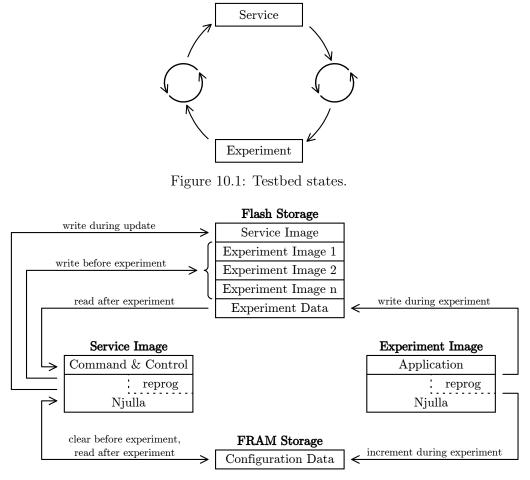

| 10.1 | Testbed states.                                                                                        | 105 |

| 10.2 | Flow of data between service and experiment images                                                     | 105 |

| 10.3 | Active part of stacks for different roles in testbed                                                   | 107 |

| 10.4 | Frame format                                                                                           | 107 |

| 10.5 | Testbed command instruction set                                                                        | 109 |

| 10.6 Parameters of an energy harvesting power subsystem                                           |

|---------------------------------------------------------------------------------------------------|

| 10.7 Experimental setup for measuring routed transmission time $114$                              |

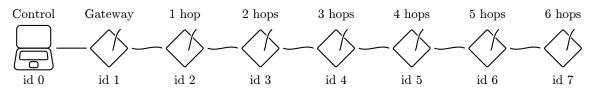

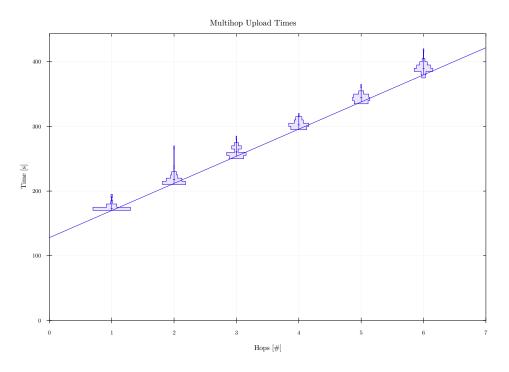

| 10.8 Full-program image upload times                                                              |

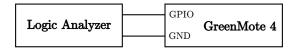

| 10.9 Experimental setup for measuring single mote reprogramming time.115                          |

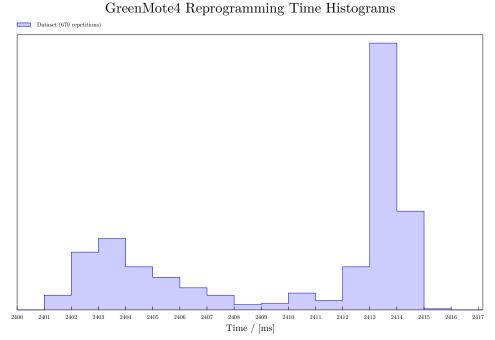

| 10.10Histogram of reprogramming time                                                              |

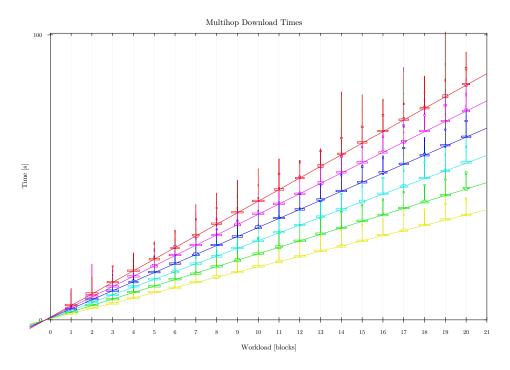

| 10.11 Multihop download times. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 118 |

| 10.12Best-case download models                                                                    |

|                                                                                                   |

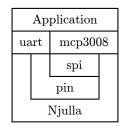

| 11.1 Stack for MCP3008 support                                                                    |

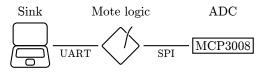

| 11.2 Experimental setup for lowlevel debugging example 125                                        |

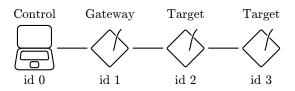

| 11.3 Experimental setup for highlevel debugging example                                           |

| 11.4 Physical id to network id node mapping                                                       |

| 11.5 Changes in state as a bug manifests as an anomaly                                            |

|                                                                                                   |

| B.1 Highlevel overview of the PhonePower design                                                   |

| B.2 Pseudocode for sampling the PhonePower board                                                  |

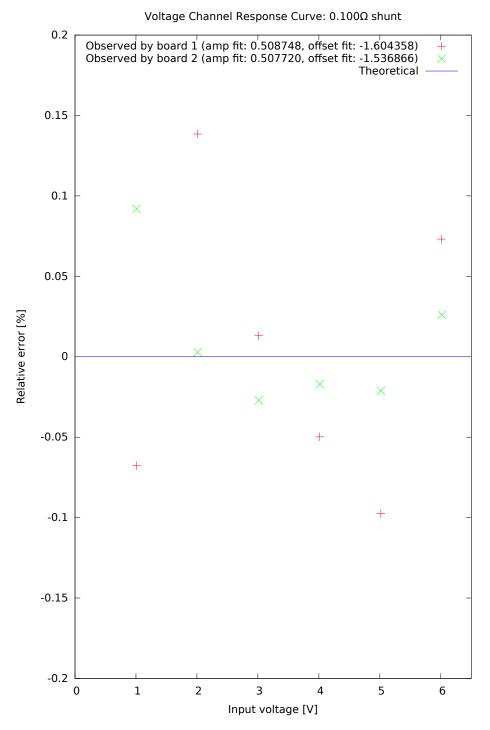

| B.3 Calibration result for the current channel of two PhonePower boards.152                       |

| B.4 Calibration result for the voltage channel of two PhonePower boards.153                       |

### Chapter 1

### Introduction

### 1.1 Thesis Context

This dissertation is the conclusion of my work as a PhD student at the IT University of Copenhagen (ITU) and DELTA<sup>1</sup>. DELTA provided most of the funding as well as the problem, ITU provided the academic framework. My time was split accordingly, resulting in around 2/3 going to DELTA and 1/3 to ITU.

DELTA is a Danish company with 70 years of expertise in electronics, light and acoustics. It exists as a conglomerate of earlier and more specialized institutes. DELTA is mainly a test and consultancy house selling their knowledge; primarily to the danish industry. In particular, DELTA designs and performs electromagnetic compatibility (EMC) and highly accelerated lifetime tests (HALT).

Their deep roots in the Danish technological history has earned them the role of a GTS institute. This is a Danish construction wherein private companies are awarded contracts by the Ministry of Science, Technology and Innovation to perform research and disseminate the resulting knowledge. There are nine such institutes; each covering different areas of technology.

In late 2009, DELTA was awarded a 3 year contract to offer services in wireless sensor networks (WSN) for long-term environmental monitoring. Danish SMEs<sup>2</sup> were the main target. It was decided to power the sensor nodes through ambient energy harvesting to eliminate the need for battery replacement. For this purpose solar, thermal and vibrational harvesters were to be considered. The focus was on an energy harvesting regime where the production is smaller than the sleep consumption of the hardware. An energy storage is thus introduced and sub-

<sup>&</sup>lt;sup>1</sup>http://www.madebydelta.com

$<sup>^{2}</sup>$ SME is an abbreviation for small and medium-sized enterprises.

jected to charge-discharge cycles, often with extremely asymmetric components. Depending on the specific setup it may take weeks to charge and perhaps a second to discharge. The discharge is what powers the sensor node. To be cost-effective these harvesters would need to be scaled to produce just enough power. This lead to a need for precise testing facility, a testbed. Due to the environmental link of the harvesters this testbed needed to be located outdoors. So the overall question for my work was: How should a testbed be designed, implemented and operated so that a range of different danish SMEs can experiment with long term data acquisition infrastructures based on energy harvesting solutions?

### **1.2** Data Acquisition Infrastructure

In order to put this work in context, let us look back in the history of data acquisition. In the old days, those who wanted to understand a greater part of the world they lived in would make observations and scribble them down. Over time these records would provide them – as well as those who followed – with a body of evidence significant enough to formulate models of the observed phenomena.

Metrics are based on comparison with yardsticks. Temperature used to be metered using a fluid with a known coefficient of expansion, weight by comparison to agreed upon reference weights. Contraptions performing these comparisons with easily observable results are known as instruments and they produce the data we are so keen to acquire.

Field biologists would hike to their lake of interest and spend considerable time and effort creating what is essentially a time series dataset. Their tools were instruments for measuring their phenomena of interest (time being one of them), pen and paper. The process required much labor and was associated with multiple sources of potential errors; the instrument had to be *sampled*, the value written down, later read and finally used in calculations. The process was flawed, but the results were valuable, and the planning and execution did not require much theoretical background beyond that of the phenomena in focus.

The labor requirement was mitigated by the introduction of dataloggers. In the beginning strips were used for storage, either for stamped values or for graphs. Both removed some human error from the process. The graphs limited these to deployment errors but didn't result in a raw dataset. The relative ease of post-processing was traded off for a visual result that everybody could relate to. Over time the dataloggers have evolved with technology and today we can store digitally, sometimes even in open formats. This eliminated the need for transcribing the logs to a processable format. Because dataloggers operate autonomously they

need to be tailored to a specific sensor or sensor interface. As a result today a wide gamut of dataloggers are in use to cater for the varying requirements of the sensors in use. Human errors are reserved mainly to deployment, but also result from the added complexities of having to deal with a layer of abstraction on top of the instruments sensor.

Over time variations over the datalogger theme evolved. Some added wireless capabilities, and some allowed for configuration of how and when to sample. While each of these variations have their place today, some have reached a state where they can be seen as regular small computers with programmable logic, storage and communication. The feature space and number of potential clever applications have exploded. They can be networked to make macroscopes; pseudoinstruments covering multiple sensor sites [67, 63]. They can perform adaptive sampling based on real-time processing of sensor readings[10]. They can monitor their own health and report on potential problems [3]. As such, a well thought out network of sensors may carry little to no maintenance and processing penalty. This shift opens up for much denser deployments given a low enough per-node price. Research has thus primarily been based on what has become known as mote-class devices<sup>3</sup>. These are computers of severely limited resources on all accounts. The constraints include memory size, processing speed, storage size, wireless communication speed and reliability, and power budget. They can be assembled to form wireless sensor networks.

### 1.3 Problem

The field biologist used to need little or no knowledge of her instruments to deploy them in the field. Likewise, facility management is used to deploying sensors or data loggers that they know nothing about to verify the quality of the indoor climate. With wireless sensor networks, the situation is significantly different. The sophistication of the instrumentation platform makes it hard to envisage a turnkey solution. So far, all sensor network deployments have required significant manpower in terms of design, programming and debugging (both at hardware and software levels)<sup>4</sup>.

<sup>&</sup>lt;sup>3</sup>While the origin of the term <u>mote class</u> is hard to track, the term <u>mote</u> was coined by Kris Pister in the Smart Dust project proposal [52], back in 1997. The importance of <u>classes</u> of computer systems was theorized by Gordon Bell [5], in 2007. Gordon Bell mentions the wireless sensor network class, which we now refer to as mote class.

<sup>&</sup>lt;sup>4</sup>The programming culture has not been standing still while sensor networks have evolved. There has been a general trend of continuous lowering of the perceived level of programming languages. Today within most fields of computer science C is considered a low-level language. It didn't use to be. While electrical engineers are likely to continue regarding assembly language high-level computer scientists and – even more so – their students are on the move. This has to be considered when designing systems that are going to require maintenance for years to come.

TinyOS[44] emerged ten years ago as a programming framework for mote class devices and quickly became dominant in the wireless sensor network research community. Arch Rock was founded to commercialize turnkey instrumentation solutions based on mote-class devices programmed with TinyOS. While Arch Rock achieved very significant engineering results, it did not succeed in providing a one size fits all mote-based instrumentation infrastructure. The Arch Rock team has been integrated in the Smart Grid division of Cisco and thus develops solutions tailored to a single domain.

Still, the illusion of universality lives well in large parts of the sensor network research community. It is not rare to read papers where it is assumed that (i) mote-class devices form a uniform class of devices for wireless sensor networks (or the Internet of Things) represented by Telos-B or Epic designs, or (ii) that TinyOS is an operating system well suited for mote-class devices.

So, should we rely on a TinyOS based testbed for DELTA's customers? Or put in a more general context: Is TinyOS a universal framework for programming any form of sensor network applications on top of mote-class devices? Equally important: How to efficiently support rapid prototyping for a range of different solutions for energy-havesting based sensor networks? In other words: How to make it efficient and easy to deploy and reprogram mote-class devices in the context of a testbed designed for the energy harvesting regime? And in the first place: How to characterize the energy harvesting regime for long term environmental monitoring? These are the questions at the heart of this dissertation. More specifically, I focused on the following two problems:

- **Programming Framework for Mote-Class Devices**: Is TinyOS well suited for programming any complex sensor network applications on any form of mote-class device? More interestingly, what distinguishes the sensor network regimes where TinyOS is a good fit from those where it is not? In general, what are the dependencies between hardware and operating system design? What are the dependencies between the application requirements and the mote design space? What are the specific requirements from the energy harvesting regime?

- A testbed for the energy harvesting regime: A requirement from DELTA was that the testbed should make it easy to rapidly prototype new applications. I chose to focus on two complementary aspects of rapid prototyping on sensor networks: (1) the ease of debugging and (2) the ease of mote reprogramming:

- 1. For a system to be easy to debug it needs to appear (and be) simple

In five years time how easy will it be to find a graduate student qualified to maintain complex C code? What can we do to lower the burden of code adoption?

to the developer. This simplicity depends on system complexity and observability. The complexity of a system depends on the involved components and the connections between those. Sometimes the complexity can be lowered by defining subsystems encapsulating – and isolating – subgraphs of this component graph. However, as long as the understanding of the whole depends on the understanding of a specific component, complexity is dependent on the observability of the internals of this component. The concept of subsystems trades observability for simplicity at the risk of providing a false sense of low complexity. Good tools can help a developer make sense of complexity, thus shifting the tradeoff. Examples include visualizations and execution traces.

2. Reprogramming a mote is the act of programming it by means of logic implemented on the mote itself. This is in contrast to the situation where a JTAG or similar programmer is used to stream an image to mote ROM. The ability to perform reprogramming allows us to perform remote updates of the software running on motes without the requirement of a linked programmer. This extends the solution space for experimentation on motes deployed in a remote testbed.

### 1.4 Approach

It is important to recall that both the problem I tackled during my thesis, and the approach I took were heavily shaped by the requirements and the constraints imposed by DELTA. My role there was to design and implement the wireless sensor network testbed. It was feared that instrumentation would affect the operation of experiments to such a degree that the results would no longer be representative of the reality. The approach was thus to limit the amount of instrumentation to a bare minimum. I designed GreenLab[35] – a prototype testbed – and implemented an initial version of it, relying on TinyOS for programming the mote class devices. Due to the combination of a dependency on Blip[31] and the use of a MSP430f1611 microcontroller (the first design was based on the Epic[16]), there was very little memory headroom on the devices. This caused DELTA to design a new board based on a different microcontroller of the same MSP family, i.e. the MSP430f5437, and I began porting TinyOS for the new board.

This task turned out to be significantly more time consuming than expected. The problems with TinyOS - along with the expectations of ports to a range of different platforms in the future – caused DELTA to look for other options. As a result DELTA changed strategy and I began to work on a new framework called **Njulla** to replace TinyOS for DELTAs purposes. The main areas of focus were

portability, ease of debugging and performance. The goal was to reach a tradeoff which was better suited for the project than TinyOS had been. This goal was assumed to be within reach due to the narrower operational space associated with energy harvesting of sub-sleep power levels. This is not the story of the new framework, but it is the story of the thoughts and design decisions that went into it. The Njulla framework for DELTAs motes was built with ease of debugging as the leading design principle. The framework was designed, implemented, tested and used for experiments. In each of these phases we have learnt lessons that are reported in this manuscript.

I also designed GreenLab, a wireless sensor network testbed for the energy harvesting regime. What distinguishes this from other testbed scenarios is the degree to which experiment results are fragile regarding external influences on the power budget and – due to the long charge-discharge cycles – the lesser significance of the temporal overhead of the test apparatus. The first incarnation of GreenLab was implemented on top of TinyOS[35]. After the departure from TinyOS I reimagined GreenLab with ease of debugging in mind and implemented it on top of Njulla. How the ease of debugging fits into the testbed is described in this manuscript.

The method used is taken from experimental computer science[13]. Throughout the design, implementation and experimental work that constitute the core of this thesis, I have formulated hypotheses, and then directed effort at trying to confirm or falsify them qualitatively, or quantitatively when appropriate. Experimental apparatus is constructed around the system under test (e.g., the Njulla framework or the GreenLab testbed) and experiments are performed to observe the behavior of that apparatus.

The evaluation is rooted in the problem: Allowing SMEs to easily prototype energy harvesting sensor networks. For Njulla this is done qualitatively for portability and ease of debugging, and quantitatively for performance relating to the typical sub-sleep energy harvesting scenario: Boot from full off state, sample a sensor and send the resulting value over a radio link. To reveal less contextspecific properties of the performance I also evaluate low-level pin and serial operation. For GreenLab I measure individual components involved in the operation of the testbed: Upload of image, switch of image and download of produced data. I evaluate this in the light of the typical use case of the testbed.

### 1.5 Contribution

The contribution of this dissertation mainly falls into three categories:

- 1. **TinyOS critique**. Based on my experiences porting TinyOS, and the experience of my research group at the IT University, I revisit the space of sensor network design regimes to distinguish those where TinyOS is a good fit from those where it is not. The lessons learned offer a new angle on the evolution and the impact of TinyOS, and some insights about the design of future network embedded operating systems aiming at large scale adoption.

- 2. Design of the Njulla Framework and the GreenLab testbed. With the design of Njulla, I took the option of a simple programming framework that could be easily ported and easily understood by new developers. Part of my contribution is the systematic description of the dependencies between hardware design and programming framework design. The goal of the testbed is to allow for experimentation on sub-sleep energy harvesting motes. With Greenlab, the key design decision was thus to limit interference with the power budget imposed by the energy harvesters. Accordingly, limiting the overhead of instrumentation was a key design parameter. This was accomplished by avoiding the use of a backchannel (e.g., an ethernet cable or a second mote).

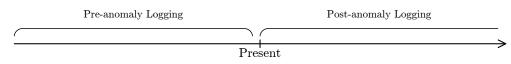

- 3. Reflections on the ease of debugging. The ease of debugging comes down to the effort required – when presented with an anomaly – to track down the cause of this anomaly, come up with a solution for removing it and implement that solution. The main component of this is the process of gaining enough perspective to reason about the cause. In this thesis, I reflect on the elements of the programming framework design that make it easier to avoid anomalies, and to detect and correct those anomalies that cannot be avoided.

#### 1.6 Thesis Structure

This dissertation is organized in two parts: The state of the art in Part I and the contribution in Part II.

The state of the art contains a description of mote-class hardware in Chapter 3. The goal is to give the reader a deep understanding of the characteristics of moteclass devices. In Chapter 4, I then review the characteristics of mote-class devices programming. I identify a set of trade-offs in the design of such programming framework and discuss the design decisions taken by two existing frameworks: TinyOS and Contiki[14]. In Chapter 5, I quickly review existing testbed solutions and focus on the reprogramming solutions that have been described in the literature. I conclude this part with a summary of the design decisions that DELTA had to take in terms of mote hardware, mote programming framework as well as testbed.

The contribution part is composed of a critique of TinyOS in Chapter 8, followed by the description of the Njulla programming framework in Chapter 9 and of the Greenlab testbed in Chapter 10. Last but not least, I discuss the lessons learned in terms of ease of debugging in Chapter 11.

The dissertation is concluded in section 12.

# Part I

# State of the Art

### Chapter 2

## **Energy Harvesting**

Energy harvesting – or scavenging – is the process of converting ambient energy into electrical energy that can be used for powering electronics. Electrical energy can be extracted from light (photovoltaic panels), temperature differences (peltier element), vibration (piezoelectric effect, electromagnetic generators), radio waves (antenna) and biological processes of plants[2, 29] (pH). Depending on the context one can choose to include the charge and kinetic energy emitted by isotopes[39] and microbial fuel cells[32]. The goal is to create perpetual deployments.

When used to power motes the output of a harvester can be classified based on its magnitude relative to the operational modes of the mote:

- *Plentiful production* The harvester generally produces more power than the mote as well as any attached sensors or actuators can consume. The mote can stay active over extended periods.

- Sub-active production The harvester produces less power than the mote consumes when active, but more than it consumes in sleep mode. The mote needs an energy storage and has to enter a sleep mode (or power off) to keep the storage from emptying.

- Sub-sleep production The harvester produces less power than the mote consumes while sleeping. The mote needs an energy storage and has to power off to keep the storage from emptying. Due to the low output of the harvester and the inefficiencies of the energy path it can take weeks to collect enough energy to do something useful.

This dissertation is mainly dealing with energy harvester setups that have subsleep production. Focusing on such energy harvesters was a decision from DELTA, on which I had no influence, and that I had to comply with. To support this,

Figure 2.1: The generic energy path of an energy harvesting node.

electronics is added to supply power in bursts. This results in the whole system operating in charge-discharge cycles. Low-power modes can not keep the mote from running out of energy; only delay the cycle. Instead the mote needs to go through the boot process every cycle.

Figure 2.1 illustrates the energy path of an energy harvesting node. The harvester generates electrical power. Depending on the harvester used, this may need to be rectified. The voltage is then scaled to fit the operational envelope of the mote and stored. The operational state of the mote is controlled through a window comparator. Each of these steps will be briefly described in the coming sections.

### 2.1 Harvester

Transducers are used for harvesting ambient energy. Some produce a direct current while others produce an alternating one. Photovoltaic arrays generates a direct current. The configuration of the array determines the balance between current and voltage: connecting cells in series will multiply to voltage while connecting them in parallel will multiply the current. Some electromagnetic generators are essentially magnets suspended in a spring and wrapped in a coil. When momentum causes the magnet to oscillate, the coil observe a change in magnetic flux. This change induces an electric current which alternates with the oscillations.

Some sources are relatively stable (e.g., pH in a tree) while others depend on prevailing conditions (e.g., solar and wind). This brings a new set of challenges, mainly (i) how do you take advantage of significant in-network variations in available energy?, and (ii) If the cycle of each node in the network is highly dependent on the local conditions, how do you synchronize nodes?

A network of solar powered nodes could be programmed to route around shadows in order to shift loads to nodes with excess energy. UCLA are doing this with their Heliomote[54]. They are working on sub-active power production.

One solution to the synchronization problem is to operate in a star topology or have a backbone of nodes on stable power. Prabal Dutta's group has uses a similar approach where energy harvesting leaf nodes uses a real-time clock to define communication windows and use these if they have enough power[72].

### 2.2 Rectifier

For harvesters producing alternating current, a rectifier is needed. Without the charging will average to zero. For harvesters producing a direct current, the rectifier should be avoided.

### 2.3 Voltage Scaling

Some harvesters produce very small voltages and others produce high ones. These need to be scaled (DC-DC converted) so that they can be used to charge the storage to a sensible level. This level is within the operating conditions of the mote. This problem has drawn a significant amount of research from the perspective of electrical engineering.

Generally speaking, the solutions are using switching converters based on capacitors or inductors. The switched capacitor solutions are called step up/down converters. A step-up converter works by charging capacitors in a parallel configuration, reconfiguring them to a serial configuration for discharge and the starting over again. The step-down variant reverses the operation. Buck and boost are two popular basic topologies of inductor-based converters.

The operating efficiency of a photovoltaic array depends not only on the input conditions (temperature, light spectrum and -angle) but also the output conditions (the applied load). By adjusting the load it is possible to locate an optimal power point. This is the voltage/current combination resulting in the highest amount of power being transferred from the storage to the mote. However, the maximum power point depends on the input conditions as well. The situation is similar for other harvesters. Most of the research being done relates to tracking the maximum power point of harvesters, and scaling the voltage accordingly.

### 2.4 Storage

Rechargeable batteries have are subject to physical deterioration, which is triggered by recharge cycles. Although they are typically rated at a few hundred charge cycles, they can handle many more shallow cycles. For long-time deployments this is still considered a problem. Batteries also react negatively to low temperatures. Lithium batteries require 4.2V in order to charge. If the mote can be run on half of that, then it may be efficient to scale down the voltage between the storage and the mote.

Supercapacitors are an option. They are large-capacity capacitors at a comparatively small size. However, the leakage current is dependent to the energy level. This is a continuous flow of current to ground through the capacitor and represents the charging level needed to keep the charge.

The Prometheus[34] system uses two energy storages. The first one is a super capacitor and it is used to take the frequent charge cycles. The second is a Lithium battery used as a backup. Logic in software determines when to power the mote through the primary storage and when to power it through the secondary one. It also determines when to charge the secondary storage from the primary, thus limiting the charge cycles seen by the battery and extending its life. Prometheus is working on sub-active power production.

### 2.5 Window Comparator

The output of the window comparator depends not only on the input but also on the current state. This characteristic is known as hysteresis. The window has a high and a low threshold. If the input is above the high threshold then the state is 'on'. If the input is below the low threshold then the state is 'off'. If the input is between the thresholds then the state stays the same. The output mirrors the state so that the mote is turned on when the state is 'on'.

The input to the window comparator is the voltage level of the storage. The two thresholds obviously need to be within the operational range of the mote. Furthermore, as the mote is likely to be the most efficient at low voltages it makes sense to place the low threshold close to the low end of the operational range. The high threshold should span enough capacity to power the mote through the longest possible single cycle. It also makes sense to match the high threshold to the voltage scaling, as this will increase the efficiency of the first part of the energy path. Here, efficiency on one side of the storage is traded for efficiency on the other.

Work was done at DELTA by another PhD student to implement dynamic thresholds[66]. This work replaces the comparators with AD conversions by the main microcontroller. The microcontroller wakes up periodically, samples the voltage level and then decides what to do. Two scenarios are evaluated: One where the wakeup is from sleep and one where it is from off. After 6.2s it is preferable to turn off the microcontroller. With the microcontroller controlling the thresholds, it opens up for complex window setups.

### Chapter 3

### Mote Hardware

Wireless sensor networks are built using multiple mote class computers. This class is not officially defined, but the following properties apply to a wide range of existing motes [28, 7, 6, 16, 53, 38].

- *Power Source* Around 20kJ for a pair of AA batteries or typically < 5mJ for motes on harvested energy.

- **Processor** 16-32 bit microcontroller (MCU) running < 80MHz.

- *Memory* RAM+ROM of  $\leq$  512kB.

- *Storage* < 32Mb of storage on a serial connection.

- *Communication* A radio 1kb/s 2Mb/s ranging up to several hundred meters, depending on conditions.

- **Sensors Interfaces** Support for analog and digital (SPI, I<sup>2</sup>C, RS232) sensors.

The MCU has on-chip memory, timer, communication and analog-to-digital conversion (ADC) modules. Everything else is connected through pins. The following subsectioning is an attempt at describing mote class platforms in a general way. A few details may be specific to the TI MSP430 series of microcontrollers. Other implementations will be different, but comparable.

### 3.1 Power Source

Active silicon converts power to heat. Antennas converts power to radio waves. Leds convert power to light. The consumption of each hardware component is defined by its state. The radio can be sleeping, in receive mode or sending. Each have different power profiles. The send operation have a profile depending on frame size. Functional units consume power when active. Among others, this includes the USARTs and the ADC.

When operating on a wall socket most deployments dont care about consumption; there are plenty of other problems to spend resources on. Batteries have a fixed amount of energy. Conserving the available energy increases the time a mote can stay operational. Techniques to lower the consumption includes

- Keeping functional units off when not in use.

- Keeping external components off or in sleep mode when not in use.

- Keeping track of the lowest possible sleep mode and have the microcontroller enter it when it would otherwise spin.

- Duty-cycle the radio, typically by employing low-power listening.

When sub-sleep energy harvesting is employed the regime changes again. Energy harvesting promises limitless energy<sup>1</sup>, but only delivers it at little power. A window comparator and some energy storage system is used to provide the energy at a useful level of power, but only for a short period at a time. This makes things more complicated. Each of these chunks are seen by the mote as a power cycle. The energy storage employed by the harvester needs to be scaled to match the maximal amount of energy needed within a single power cycle. An application could sample a sensor and store the result to flash and transmit it over a radio. A strategy of matching a sample-store-transmit sequence to a power cycle would consume some amount of energy. Having a strategy which performs a samplestore sequence for 9 cycles followed by a single sample-store-transmit cycle is not going to save anything: The storage still have to match the sample-storetransmit sequence. Instead, one could perform the sample-store sequence for 9 cycles and then have a load-transmit sequence. This would lower the maximum required energy to either that of sample-store or that of load-transmit, whichever is largest.

### 3.2 The Analog in Digital

Digital logic is implemented through abstractions on top of analog circuitry. It operates at a logic level (often 3.3V or 5V), meaning that digital high is coded

<sup>&</sup>lt;sup>1</sup>Practicalities dictate otherwise.

Figure 3.1: Anchoring of ground planes.

as this value and digital low is  $0V^2$ . In reality everything above some threshold is interpreted as high and everything below as low. The interface of an integrated circuit (IC) expects clear highs and lows on the inputs, and in return guarantees clear highs and lows on the outputs.

Those voltages are measured relative to a ground plane. 0V is in the plane. Two motes have different ground planes unless the two planes have been anchored to each other. Typically one connects the two ground planes in order to agree on logic levels. However, if motes  $M_A$  and  $M_B$  are both on 3.3V logic levels and the ground of  $M_A$  is connected to high on  $M_B$ , then  $M_B$  will see a high from  $M_A$  as 6.6V. This scenario is illustrated in figure 3.1.

A pin is said to be floating as long as it is not anchored to something well defined. When a pin floats its voltage is highly susceptible to outside influences. For this reason it is common to observe a 50Hz signal on floating pins (in 50Hz grid areas) when measuring equipment is attached.

A pin can be anchored, typically using a *pull-up resistor* (to logic high) or a *pull-down resistor* (to logic low). A resistor to anything anchored will do though. The idea is to weakly pull the line towards something. Logic can then easily pull the line in the other direction if needed.

### 3.3 Mote Channels

Each I/O pin is associated with a configuration that defines which and how functionality is exposed. The configuration has four properties, each mapping to a binary universe of values.

1. Route  $Pin.Route \mapsto \{GPIO, FUNC\}$ The universe of values contains GPIO (for low-level usage) and FUNC (for routing to a hardwired functional unit).

<sup>&</sup>lt;sup>2</sup>This is the case for *active high* lines. The situation is reversed for lines which are *active* low. This property is called the *active state* of the line. Active low lines are usually marked with an overline (e.g.  $\overline{CE}$  for 'chip enable').

Figure 3.2: Examples of pin to functional unit routing.

- 2. Direction  $Pin.Direction \mapsto \{Input, Output\}$ The universe of values contains Input (for reading) and Output (for writing). This is relevant only when  $Pin.Route \mapsto GPIO$ .

- 3. Interrupt  $Pin.Interrupt \mapsto \{Enabled, Disabled\}$ The universe of values contains Enabled and Disabled. This is relevant only when  $Pin.Direction \mapsto Input$ .

- 4. **Edge**  $Pin.Edge \mapsto \{Rise, Fall\}$ The universe of values contains Rise and Fall. It specifies the type of transition that should generate an interrupt. This is relevant only when  $Pin.Interrupt \mapsto Enabled$ .

Some pins are associated with a peripheral unit such as a serial block or an AD converter. This peripheral unit is controlling the pin when  $Pin.Route \mapsto FUNC$ . If instead  $Pin.Route \mapsto GPIO$  then the pin is in GPIO mode and has a direction. When it is an *Input* pin the logic level can be sampled, when it is an *Output* pin it is set (pulled to logical high or low). While in *Input* mode it can be configured to generate interrupts on a rising or falling edge.

Figure 3.2 illustrates how pins can be routed to functional units. The top row of demultiplexers can be selected using Pin.Route. This allows each pin to be routed to a single (hard-wired) functional unit. Some pins are associated with serial communication, others with AD conversion.

A channel is a collection of wires connecting two or more hardware components. Peripherals such as radio, flash, sensors and actuators are connected to microcontrollers through channels. We use the channel layout as a way of characterizing the architecture of a mote. Section 3.7 will bring an example.

Figure 3.3: Conceptual model of an ADC unit.

### **3.4 AD Conversion**

Digital is an abstraction on top of analog, where specific logic levels are used to separate the 1 from the 0. Sensors work by reacting to some analog property, usually by generating an analog signal which then have to be digitized to be processable to a digital computer. The process of converting an analog input to a digital output is called analog-to-digital conversion or AD conversion and is performed by a module called an AD converter, ADC in short. The reverse process is typically used for actuators and is performed by a digital-to-analog converter, a DAC. A cheaper variant of the DAC is a pulse-width modulation (PWM) engine. These generate a pulsed signal where the high-to-low ratio represents the analog value. The sharp transitions may cause problems with components or humans expecting a stable value.

AD conversion is essentially a two-step process. First a signal is sampled by connecting an internal capacitor to an input. Over time this capacitor will charge to the same level as the input. The minimum time required to reach this level is a function of the size of the capacitor and the output resistance of the source we are measuring. The sample time is configured by choosing a clock and scaling it. Disconnecting the signal will end the sampling process. The last step is to convert the sampled value to a digital representation and store this in memory. This conversion is done relative to a reference. In other words, a signal outside the reference frame will not be distinguishable from a signal at the edge of the reference frame. Most microcontrollers provide one or more internal references as well as an external one. Figure 3.3 illustrates a basic sample-hold-convert system.

There are different ways of performing the conversion step. The entire conversion could be performed in a single cycle by using a flash ADC, but that would require  $2^n - 1$  comparators for *n* bit resolution. This represents a lot of space on the silicon, depending on *n*. A successive-approximation ADC perform what is essentially a binary search. A window representing the sample value is iteratively narrowed in by feeding the median value (representing the next bit) through a DAC and comparing to the sample. This solution takes up little silicon but is slow and – because of the iterative approach – fragile to a fluctuating reference. Other methods exists providing different trade-offs between conversion resolution, sampling frequency, tolerance of reference fluctuations and required die area. A result of these constraints is that microcontrollers tend to have few (e.g. a single) ADC units.

Because of the limited number of ADC units present in microcontrollers it is a common practice to allow multiple pins to be routed to these units. That way many analog sensors can be connected and multiplexed at will. The multiplexing logic is relatively cheap.

### 3.5 Serial Communication

Serial communication can be accomplished by doing GPIO operations. A stream of bits have to be transmitted by one end and received by another. The transmission is done by setting a GPIO pin high or low. The reception is done by sampling a GPIO or detecting transitions on it. But how do we know when the line is active (that something is being transmitted)? Sampling the line will always give some value as it has a physical state. Either we add a protocol or we involve a second line. The protocol could escape the resting value or encapsulate transmissions in predefined patterns.

How do we know when to sample? Some mechanism for synchronization is clearly needed. A common agreement of bitrate solves the problem of separating individual bits, but the two ends need to have (and keep) synchronized clocks for this to work. Clock drift is influenced by temperature and even clocks from the same series will exhibit different drift under matching external conditions. Due to drift a synchronization mechanism relying only on bitrate will have a *bit error rate*. To minimize this one can add and sync on regularly occurring special bit patterns. This will also result in the two ends being initially synchronized. Another option is to involve a dedicated clock line driven by the master end. In this case an agreement of when to set the value (e.g. on rising edges) and when to sample it (e.g. on falling edges) is needed. Accordingly an active clock means that there is a transmission. The maximum clock speed is limited by the time the receiver needs to process the incoming data.

So far we have looked only at links between two ends, but the concept can be extended in a number of beneficial ways. A *bus* connects multiple endpoints. By extending the protocol of the transmitted bitstream one can target a named endpoint, thus eliminating the need for a bus master. That of course increases the complexity of the protocol-handling logic. This any-to-any model is rarely necessary and thus a simpler solution is often used where a single master is connected to multiple slaves. All slaves receives all transmissions but each slave

Figure 3.4: UART frame format.

is connected to the master with an additional *slave select* line. The state of this line determines whether the slave reacts to the data line(s). For this to work exactly one slave select line has to be active when requesting a response.

Most microcontrollers provide serial units to automate these tasks and hide some of the complexity. The smallest unit of transmission is a single byte, but sometimes bulk transfers (of larger amounts of data) are available. The following subsections will give examples of different types of serial communication. On some microcontrollers each functional block implements exactly one of these, on others they can be configured to implement any of a subset of them. The common property is that the number of these units is limited.

#### 3.5.1 UART

The term UART is ambiguous as it is used as a general name for a serial functional unit as well as a specific protocol. In this section we refer to the latter meaning. The UART protocol has been widely used over RS232 links for bidirectional communication, and is the most common link between a mote and a general-purpose computer. Here it is adjusted to follow CMOS/TTL logic levels. The two ends have to agree on bitrate. In the most simple version two lines are used for full-duplex:

- *master-to-slave* Data flowing from the master endpoint to the slave endpoint.

- *slave-to-master* Data flowing from the slave endpoint to the master endpoint.

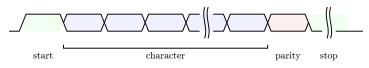

The unit of transmission is a *character* typically spanning 7 or 8 bits. The format has an optional parity bit to provide robustness towards bit errors. The two ends needs to agree on the semantic of the parity bit. To provide a means of synchronization the data in wrapped by a single start bit and a few stop bits, typically 1-3. The frame layout is shown in figure 3.4.

#### 3.5.2 SPI

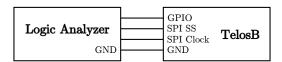

The Serial Peripheral Interface (SPI) bus is used to connect a single master endpoint to one or more slave endpoints. The bus employs four lines:

- **SS** The slave select line. Slave endpoints reacts to communication if and only if their SS line is active. One line per slave is required.

- **MOSI** The master out slave in line. This carries the bit stream from master to slave.

- *MISO* The master in slave out line. This carries the bit stream from slave to master.

- *CLK* The clock line. During each period a single bit is transferred in each direction. The master provides the clock. While slaves endpoints have a maximum frequency there is no strict minimum and there is no need for it to be static.

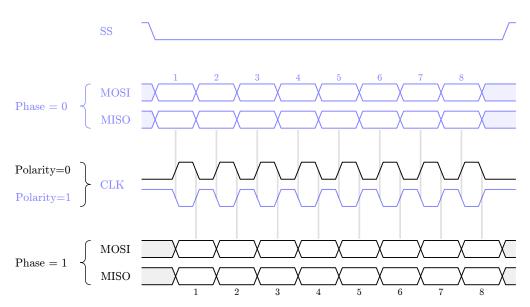

To support the mode of operation each endpoint has two registers; one for receiving and one for transmitting. At the beginning of the clock period one bit is shifted out of the transmit register and the outgoing line is set accordingly. In the middle of the period the ingoing line is sampled and the resulting bit is shifted in to the receive register. The unit of communication is a byte. As a result any response on the MISO line is delayed at least 1 byte. To deal with this it is common for higher-layer protocols to pad commands with blank bytes.

As with RS232 there are variations of the standard, but only two properties vary. The first is the clock polarity which defines the resting state of the clock line. A polarity of 1 means that the clock line rests in the high state and is thus active low. The second is the sampling phase which which defines which edge to sample on. A phase of 0 means that sampling should be done on the first edge of the clock signal. Figure 3.5 summarize these settings and highlight a single configuration.

#### 3.5.3 $I^2C$

The inter integrated circuit bus  $(I^2C)$  is an any-to-any bus. Mote-class hardware usually use it for the one-to-any part of this quality as well as its low requirements regarding linecount. It only occupies two lines and adds some extra complexity to make it work. The lines are:

• **Data** This is a half-duplex line. For this to work all endpoints needs to agree on who is transmitting. A protocol is employed to target named

Figure 3.5: SPI line transitions. The  $\{Phase \mapsto 0, Polarity \mapsto 1\}$  configuration is highlighted in blue.

endpoints. This provides the same functionality as the slave select lines from SPI.

• *Clock* One bit is transmitted on the *Data* line per period. Controlled by the active master.

In a single-master setup arbitration is easy. At the end of a request from a master the named slave is supposed to answer. In a multi-master setup all master endpoints employs two techniques to keep the line free of corruption.

- *Carrier Sense* Every master monitors the bus for start and stop bits. This way no master will begin transmitting while another is in session. For this technique to work there needs to be some time in between the two masters trying to start communication. When that is not the case another technique is employed:

- *Feedback* Two masters grab the bus at the same time and begins transmitting. If they don't transmit the same bit sequence and this is the only case of interest then at one point they are trying to pull the line in each direction. This will result in the line going to ground. The reason for this is that the line operates in *open drain* mode where a static pull-up resistor is used to pull the line high. The line needs to actively be set low to go down. When a master switches the pin to input (to weakly pull it high), it also samples the line. If the line is low then it knows that the line is occupied and backs off.

# 3.6 Peripherals

Many applications of motes come with severe restrictions on power. Sometimes it is even necessary to power cycle individual components by use of digital switches. They often toggle multiple lines so that parasitic currents – where part of the circuitry is fed through lines designed for signals – can be avoided. Functional units within the microcontroller can be turned off and sometimes external components (radio and flash) can be as well.

Motes should be small (to limit form factor and energy consumption) and cheap. For the MCU this translates to a small die and few pins. Both are reused where possible. Pins have multiplexed functionality and may need to be arbitrated. Many can be routed to a single AD converter. Serial units may support different types of communication but only be capable of driving one at a time. Multiplexers are digital switches which selects one among multiple lines.

Due to the way physical components are arbitrated to provide functionality it can be hard to reason about differences in mote architecture. In an attempt to alleviate this we introduce the concept of a *channel* representing the dependency of a bundle of lines. We furthermore describe mote architectures as graphs of links.

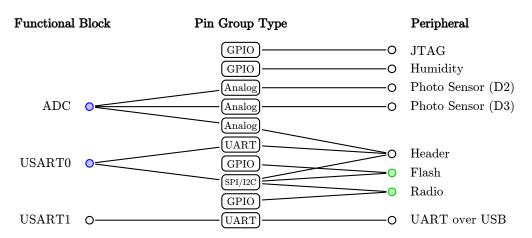

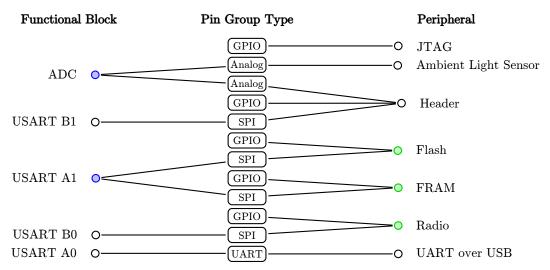

## 3.7 Case Study: TelosB

To highlight the consequences of the architectural choices regarding channel layout we analyze the TelosB[53], one of the most popular mote hardware platforms. In this example we focus one three functional blocks within the MCU as well as all major components on the PCB. The MSP430f1611 of the TelosB has a single ADC and two USARTs (each providing hardware support for a selection of serial buses). It also have limited clock and pin interrupt capabilities, but we refrain from involving these to keep the model simple. Figure 3.6 contains a channel dependency graph of the involved mappings.

In addition the the MCU the TelosB contains:

- **JTAG** A programming and debugging interface connected through GPIO pins.

- *Humidity* A humidity sensor connected through ordinary GPIO pins. The MCU has to implement a soft-I<sup>2</sup>C protocol to talk to the sensor.

- *Photo Sensors* Two photo sensors connected through pins routable to the ADC.

Figure 3.6: The TelosB channel dependency graph. Blue nodes can only operate a single edge at a time, green nodes needs all directly connected edges to operate.

- *Header* An expansion header with pins for serial communication (UART, SPI and I<sup>2</sup>C) connected to USART0 as well as some GPIO pins routable to the ADC.

- *Flash* A flash chip is connected to USART0 through SPI and has a few GPIO lines.

- *Radio* A radio chip is connected to USART0 through SPI and has a few GPIO lines.

- **UART over USB** USART1 is dedicated to an FTDI chip providing a UART connection over USB.

The USART1 is only connected by a single channel and that channel is routed to a USB connector. The USART0 is used for all other serial peripherals. Sampling a serial sensor by means of an USART cannot be done independently of flash or radio operation. This suggests that the main use case for the TelosB is to be connected directly to a general purpose computer for streaming purposes, either as a gateway or an interface to sensors. In order to use it in sample-store or sample-send scenarios this channel would have to be arbitrated. Channel arbitration does not necessarily result in significant overhead.

The added complexity does mean that the programmer needs to keep track of which channels are active and which slices of code is waiting for it. This is essentially a dependency graph. In the general case care should be taken to avoid deadlocks.

# Chapter 4

# Mote Programming

A given mote must be programmed to provide the required behaviour in the context of a testbed, or more generally, in the context of a wireless sensor network application. In this section, I review how the traditional computer systems abstractions (communication, processing/interpreter and memory [57]) are handled on mote class devices. An additional dimension which is critical for mote programming is power consumption. I cover that in a separate section. I also dedicate a section to mote debugging, which is a key aspect of productive mote programming. I conclude this chapter with two example mote programming frameworks: TinyOS and Contiki.

### 4.1 Abstractions

#### 4.1.1 Communication

On a mote, the communication abstraction relates to sensors and actuators (including radio and flash). There is a large selection of analog sensors. As we noted in the previous section, most motes have a single ADC which needs to be multiplexed. Some actuators are analog. Analog output is less common than analog input. Some microcontrollers have built-in DACs (Digital to Analog Converters), others only have PWM (Pulse Width Modulation) engines. The software interface could be the same.

Some sensors communicate results back to the mote almost immediately. Thermistors and light sensors belong to this category. Others require significant time to stabilize. The PPD42NS particle sensor uses the heat generated by a resistor to create a stable draft inside the sensor[64]. A beam of light will be reflected by particles in this draft. A light receptor is used to measure the reflected light and based on this give a value. It takes a static amount of time to warm up the resistor and it takes a dynamic amount of time (depending on magnitude of the observed phenomena) to accumulate the output of the light receptor. If a signal is small then the sampling has to cover a long period of time. Actuation may also take time, e.g. if something has to be physically moved.

We review the main mote communication abstractions in the rest of this section.

#### 4.1.1.1 Serial communication

Serial communication is normally done one byte at a time. At high speeds it makes sense to poll for completion of each byte, at low speeds one has to trade off the overhead of polling against the overhead of interrupts. The overhead of interrupts are twofold, first it takes a few cycles to set up the interrupt and second – when the interrupt is produced – two context switches will be performed: To and from the interrupt handler.

Large transfers can be performed by a DMA engine, if the microcontroller has one. Here the situation is the same as the interrupt approach except that (i) only a single interrupt in involved in the entire transfer, and (ii) the overhead of setting up the transfer is significant. In practice this is only relevant for monologues.

#### 4.1.1.2 Radio

From the perspective of the mote a radio is a combination of sensing and actuating logic. There is an interface through which commands can be sent. At the high level frames are sent to the radio, which then transmit them. Upon completion of the transmission the microcontroller is signaled through a GPIO. Upon reception the microcontroller is signaled and the frame is then transferred.

The radio can operate on different abstractions. Some radios are interfaced at a very low level. The frames have to be transferred one bit at a time at the right frequency and jitter on the lines can propagate to the antenna[45]. Other radios expose a command-based interface over a serial bus and buffer the frames. These interfaces are tolerant to imprecise timing in the code running on the microcontroller.

In practice, operating the radio is a bit more complicated as loops are involved. Before sending a frame it makes sense to do CSMA. This is a technique for significantly lowering the risk of frame collision by sampling the channel and waiting for a clear channel before transmitting. This involves polling the radio. If reliable communication is required then logic needs to be implemented to retransmit frames when no acknowledgements have been received.

#### 4.1.1.3 Multiple Streams

Motes are often directed to perform several concurrent duties. A mote could be tasked with routing data over radio while sampling a sensor to flash while sending data from flash over radio.

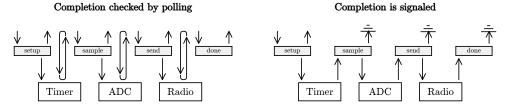

The problem is that once an operation takes time there is – generally speaking – better things to do than polling. If other operations are active at the same time work could be performed on these to increase overall responsiveness. Otherwise the microcontroller could be placed in sleep mode to save energy. Strictly serial operation is wasteful. It is easy to debug though.

There is a need for an efficient mechanism that multiplexes these streams. Hardware resources tend to have lower bandwidth than what can be processed by the microcontroller. This makes them scarce resources which should be kept under load.

#### 4.1.2 Interpreter

#### 4.1.2.1 Interrupts

Interrupts are used as a means to avoid polling. There are two problems associated with polling; (i) one has to decide on a frequency or pattern thereby trading overhead against reaction time, and (ii) while polling the program counter needs to be active thus limiting the opportunities for the mcu to enter sleep states. For many applications, the event of receiving a packet via the radio is so significant that the system designer will try to minimize the reaction time. This would yield a very high polling frequency and likely make it infeasible to enter sleep states.