# Operating System Support for High-Performance Solid State Drives Matias Bjørling

A dissertation submitted to the PhD school at the IT University of Copenhagen for the degree of Doctor of Philisophy.

Submitted: May 2015, Copenhagen

Defended: Final version:

#### Advisors:

Philippe Bonnet, IT University of Copenhagen, Denmark Luc Bouganim, INRIA Paris-Rocquencourt, France

#### Evaluation committee:

Peter Sestoft, IT University of Copenhagen, Denmark Gustavo Alonso, ETH Zürich, Switzerland Alejandro Buchmann, TU Darmstadt, Germany

# **Abstract**

The performance of Solid State Drives (SSD) has evolved from hundreds to millions of I/Os per second in the past three years. Such a radical evolution is transforming both the storage and the software industries. Indeed, software designed based on the assumption of slow IOs has become the bottleneck in the era of high-performance SSDs.

In the context of the CLyDE project, a collaboration between the IT University of Copenhagen and INRIA Rocquencourt, we recognized the mismatch between software designed for hard drives and high- performance SSDs. This thesis focuses on the role of the operating system in reducing the gap, and enabling new forms of communication and even co-design between applications and high-performance SSDs.

More specifically, we studied the storage layers within the Linux kernel. We explore the following issues: (i) what are the limitations of the legacy block interface and its cost in the context of high-performance SSDs? (ii) Can the Linux kernel block layer cope with high-performance SSDs? (iii) What is an alternative to the legacy block interface? How to explore the design space? (iv) How about exposing SSD characteristics to the host in order to enable a form of application-SSD co-design? What are the impacts on operating system design? (v) What would it take to provide quality of service for applications requiring millions of I/O per second?

The dissertation consists of six publications covering these issues. Two of the main contributions of this thesis (the multi-queue block layer and LightNVM) are now an integral part of the Linux kernel.

# Acknowledgments

The following dissertation concludes my studies at IT University of Copenhagen. It is a synopsis of six papers: (i) Three papers published and one under review. (ii) Two are workshop papers; one born out of the need of simulating SSDs and the last one (iii) was created while Michael Wei was visiting our research group December 2014. The years have gone by and its incredible how fast the time have gone. It has been a pleasure to dive deep into a topic, meet very talented researchers and explore a subject at my own pace. For all this, I can thank:

My adviser, Philippe Bonnet, for guiding me through the life of university. We have been working together since his first database course at Copenhagen University and I did not think for a second that this would be where we ended up ten years later. It has been a great ride.

Thanks to Luc Bouganim from INRIA and Steven Swanson from UCSD. The former for letting me visit INRIA and long discussions about SSDs. The latter for hosting my visit at UCSD. It was great to be part of his lab for four months. His students were very welcoming and we had a great time.

Thanks to Jens Axboe for guiding me through the industry and opening a lot of opportunities that else would not have been possible.

Freja Krob Koed Eriksen and Christina Rasmussen from the ITU PhD School. They have been a tremendous help while doing the PhD. I am grateful for having such wonderful people taking care of us *kids*.

Friends and family for encouragement and support. Especially my wife Trine, who has taken care of everything when things got busy up to a deadline and to bear with me during times when I was in my own bubble. She has been an inspiration to me on how to live a great life and always brings the best out of me.

At last, thanks to all the great lab mates: Javier González, Jonathan Fürst, Aslak Johansen, and Niv Dayan from IT University of Copenhagen for being part of a great research environment. A special thanks to Michael Wei at UCSD, that made the stay at UCSD so much more fun. I had never discussed new ideas as much as with him. Wish you all the best of luck.

# Contents

| Co                                                         | onten      | ts                                            | V  |  |

|------------------------------------------------------------|------------|-----------------------------------------------|----|--|

| 1                                                          | Intro      | oduction                                      | 1  |  |

|                                                            | 1.1        | Context                                       | 1  |  |

|                                                            | 1.2        | Solid State Drive Basics                      | 3  |  |

|                                                            | 1.3        | Problem                                       | 4  |  |

|                                                            | 1.4        | Approach                                      | 7  |  |

|                                                            | 1.5        | Contributions                                 | 8  |  |

|                                                            | 1.6        | Structure of the Thesis                       | 13 |  |

| Literature                                                 |            |                                               |    |  |

| 2                                                          | The        | Necessary Death of the Block Device Interface | 19 |  |

| Lit                                                        | Literature |                                               |    |  |

| 3 Linux Block IO: Introducing Multi-queue SSD Access on Mu |            |                                               |    |  |

|                                                            | core       | Systems                                       | 28 |  |

| l i <del>t</del>                                           | iterature  |                                               |    |  |

| 4          | I/O Speculation for the Microsecond Era                                | 44 |  |  |

|------------|------------------------------------------------------------------------|----|--|--|

| Literature |                                                                        |    |  |  |

| 5          | LightNVM: Lightning Fast Evaluation Platform for Non-Volatile Memories |    |  |  |

| Literature |                                                                        |    |  |  |

| 6          | Open-Channel Solid State Drives                                        |    |  |  |

| Literature |                                                                        |    |  |  |

| 7          | AppNVM: A software-defined, application-driven SSD                     |    |  |  |

| Lit        | Literature                                                             |    |  |  |

| 8          | Conclusion                                                             |    |  |  |

|            | 8.1 Open Issues                                                        | 92 |  |  |

|            | 8.2 Perspectives for Industry                                          | 93 |  |  |

|            | 8.3 Perspectives for Research                                          | 94 |  |  |

# Chapter 1

# Introduction

#### 1.1 Context

Millions of petabytes of data are generated each year and must be stored and accessed efficiently for business, entertainment, government or science. From the 80s until a couple of years ago, database systems have relied on magnetic disks as secondary storage.

Successive generations of magnetic disks have complied with two simple axioms: (1) locality in the logical address space is preserved in the physical address space; (2) sequential access is much faster than random access. The former axiom reflects the simple logic embedded in magnetic disk controllers. The latter axiom is shaped by the physical characteristics of rotational devices: startup costs involving disk head movement are high, while running costs involving rotation of the disk platter are low: Random accesses are slow, while sequential accesses are fast.

As long as magnetic disks remained the sole medium for secondary storage, the block device interface proved to be a very robust operating system abstraction that allowed the kernel to hide the complexity of I/O management without sacrificing performance. The block device interface is a simple memory abstraction based on read and write primitives and a flat logical address space (i.e., an array of sectors). Since the advent of Unix, the stability of disks characteristics and interface have guaranteed the timelessness of major database system design decisions, i.e., pages are the unit of I/O with an identical representation of data on-disk and in-memory; random accesses are avoided (e.g., query processing algorithms) while sequential accesses are favored (e.g., extent-based allocation, clustering).

Today, the advent of solid state disks (SSD) based on NAND flash memory has transformed the performance characteristics of secondary storage. SSDs rely on tens of flash chips wired in parallel to deliver high throughput (hundreds of MB/s to GB/s) and latency in the microsecond range. Over the last five years, the transition has been very fast from magnetic disks providing throughput of 100s of random I/O per second (IOPS), to SSDs providing hundreds of thousands of IOPS (OCZ Vertex 3) and beyond a million IOPS (Fusion-io ioDrive Octal) for a single device. Similarly, sequential throughput for a single device has increased from hundred of MB/s to GB/s.

The adoption of flash-based SSDs has created a mismatch between the simple disk model that underlies the design of today's database systems and the complex flash devices of today's computers. The CLyDE (Cross Layer Database Engine for flash-based SSDs) research project, a collaboration between the IT University of Copenhagen and the SMIS Project at INRIA Paris-Rocquencourt, was funded in 2011 by the Danish

Independent Research Council to tackle this issue.

CLyDE is based on the insight that the strict layering that has been so successful for designing database systems on top of magnetic disks is no longer applicable with SSDs. In other words, the complexity of SSDs cannot and should not be abstracted away if it results in unpredictable and suboptimal performance. This PhD project has been funded by the CLyDE project. This thesis, with the software I produced and the papers collected in this manuscript constitute a significant part of its contribution.

### 1.2 Solid State Drive Basics

Before I proceed with the focus of my thesis, I need to introduce the basics of SSD design. Note that SSD basics are covered repeatedly throughout the papers that constitute this manuscript. I describe SSD internals in details in Chapter 2, where I also discuss misconceptions about their performance characteristics.

The non-volatile storage in an SSD is NAND flash chips. They provide high performance, at low energy consumption. Unfortunately, flash chips have severe constraints [1, 4]: (C1) Write granularity. Writes must be performed at a page granularity (4KB-16KB); (C2) Erase before write. A costly erase operation must be performed before overwriting a flash page. Even worse, erase operations are only performed at the granularity of a flash block (typically 64-256 flash pages); (C3) Sequential writes within a block. Writes must be performed sequentially within a flash block in order to minimize write errors resulting from the electrical side

effects of writing a series of cells; and (C4) Limited lifetime. Flash chips can support thousands erase operations per block.

The software embedded into flash devices is called Flash Translation Layer (FTL). Its goal is to hide flash chip constraints (erase-before-write, limited number of erase-write cycles, sequential page-writes within a flash block) so that flash devices can support the block device interface. A FTL provides address translation, wear leveling and strives to hide the impact of updates and random writes based on observed update frequencies, access patterns, or temporal locality.

#### 1.3 Problem

With magnetic disks, hardware was the bottleneck in the I/O stack. Software should find interesting work to do while waiting for I/O to complete. With SSDs however, it is software that has become the bottleneck. The software that composes the I/O stack, including FTL, device driver, operating system block layer to applications, must be streamlined and possibly reorganized in order to keep up with hardware performance.

For years, the transport interface has bounded the performance of the underlying storage hardware. The advent of SSDs quickly exposed the relatively slow transfer speeds and latencies in these legacy protocols. For example, SATA/SAS limited the throughput to 300-600 MB/s.

In 2007, Intel introduced the NVM Express [13] (NVMe) protocol to fully leverage the PCI-e transport interface for storage devices. The PCI-e bus, with its 1GB/s per lane in PCI gen3 standardilization enables SSDs

to scale their throughput. In terms of latency, PCI-e roundtrip is around 1us for a 4K I/O request [3].

NVMe exposes SSD parallelism so that it can be fully utilized by host's hardware and software. The first commercially available controllers supporting NVMe were released in 2012. Today, NVMe has become the standard interface for high-performance SSD on top of PCI-e.

I have focused my work on the consequences of the introduction of high speed interfaces on system design. My core assumption is that the operating system should be redesigned to fully utilize the parallelism of SSDs exposed via NVMe. My thesis is that the operating system should remain a mediator between diverse applications and a variety of high-performance SSDs. The fundamental question is which form of mediation should the operating system perform. More specifically, I have studied the following questions:

1. Is the block device interface still relevant as a secondary storage abstraction? What are the alternatives? The block device interface hides the complexity of the underlying storage devices behind a very simple memory abstraction. System design has been based on the assumption of a stable performance contract exists across the block device interface. Such a contract ((i) contiguity in the logical address space is reflected on disk, and (ii) sequential access is much faster than random access) has driven the design of system software on both sides of the block device interface.

For magnetic drives, rigorous performance models have been extensively studied [20, 1] based on the mechanical characteristics of hard-drives (seek time, number of spindles, rotations per minute). For SSDs however, my previous work has contributed to showing the limits of SSD performance modeling. Together with Luc Bouganim and Philippe Bonnet, I showed that the performance characteristics and energy profiles vary significantly across SSDs, and that performance varies in time based on the history of accesses.

SSD performance fluctuations are a product of the characteristics of flash chips and of the complexity of the FTL that handles the mismatch that exists between the interface that the SSD exposes (read/write) and the internal interface for flash chips (read, write, erase).

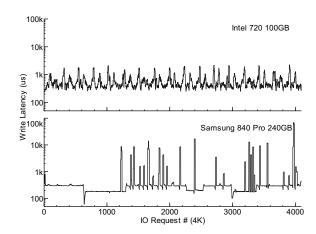

Back in 2011, Bill Nesheim, then Oracle VP for Solaris Platform Engineering, illustrated the consequences of SSD performance fluctuations during his keynote at the Flash Memory Summit [17]: "An average latency of about 1ms is irrelevant when the application is waiting for the 100+ ms outlier to complete". In 2015, this is still true and poses a significant challenge for system design.

2. What are the bottlenecks in the operating system I/O stack? How to remove them? In the CLyDE project, the initial focus lied on cross-layer optimizations between database system and SSD. However, we quickly made two observations. First, it became apparent that we could not oversee the crucial role of the operating system in the I/O stack. Indeed, as SSD latency decreases, the overhead of the operating system software stack becomes a significant part of the

time it takes to process I/Os [2]. Second, we realized that key-value stores and other types of data management systems had become important for increasingly large classes of applications and that they should also benefit from SSD performance. Here again, the operating system plays a central role in supporting various types of applications. When I started my PhD, several initiatives had been taken to improve the communication between operating system and SSD: (a) the Trim command [23, 14] had been introduced to notify SSDs of invalid sectors, (b) file-systems and applications had the option to know whether an SSD was used as secondary storage and (c) careful optimization of hot code paths for each I/O had been applied. These initiatives increased I/O throughput and lowered I/O latency. However, the Linux operating software stack still exhibited a significant overhead as it had been designed for a single core and was heavily optimized for traditional hard-drives. I thus chose to focus on the following question: How to get Linux to scale to millions IOPS and microsecond I/O latency?

# 1.4 Approach

The approach I have taken to study these problems is rooted in experimental computer science [12]. First, the core of this thesis is based on the design, implementation and experimental evaluation of operating system components. Second, throughout this thesis, I have formulated hypotheses, and then directed effort at trying to confirm or falsify them qualitatively, or quantitatively when appropriate.

Another important aspect of the approach I have taken to my thesis concerns my contribution to open source software in general and to the Linux kernel in particular. Early on in my thesis, I realized that I was fortunate to work in an area where deep changes were taking places, and that I might have an opportunity to contribute to some of these changes. In order to maximize the impact of my work I wanted to engage the industry as well as the research community. This is why I spent 4 months as an intern at Fusion-io in the summer 2012.

I had the privilege to work with Jens Axboe, previously at Fusionio, now at Facebook. Jens has been the maintainer of the Linux block layer for many years. This internship and the collaboration with Jens enabled me to establish a pattern that I followed throughout the thesis based on (1) contributions to the Linux kernel and (2) a principled design and experimental evaluation that could lead to scientific publication.

### 1.5 Contributions

This manuscript is composed of 6 publications I co-authored throughout my thesis. Together, they form a contribution that can be represented as a bottom up sweep of the operating system's I/O stack in six steps.

Step 1: We observe that the interface between SSD and the host is restricted to a narrow block interface that exposes a simple memory abstraction (read/write) on a flat address space. This interfaces leaves no space for communicating the intent of the applications that run on the host. There is thus a complete disconnect between what the disk knows and what the host knows. For magnetic disks, this disconnect

was bridged by an implicit performance contract. For SSD, there is no stable performance contract.

In the first paper, published at CIDR in 2013, we debunk some of the common myths about SSD performance. We argue that the block device interface has become an obstacle to principled system design due to the non existence of a generic performance contract. We conclude this paper by giving a vision of how database systems can efficiently interact with SSDs and we argue that a deep redesign of the entire I/O stack, including the operating system, is needed.

Step 2: Having laid the foundation for the upcoming research, we tackle the block layer within the operating system. Research papers [2, 9, 3] have shown significant overhead per I/O within the operating system. We expect that hardware performance will continue to outgrow software performance for the foreseeable future. Moving our attention to the OS, there are several parts that can be optimized.

The block I/O interface within a kernel is usually divided into several parts: (a) Device driver that handle communication to and from the block device, (b) the block layer that handle fairness, scheduling, etc. of an I/O, and (c) libraries that are exported to the user-space through asynchronous and synchronous mechanisms. The device drivers are device specific and we leave any research on optimizations to the device vendors. We instead focus on the block layer and submission/completion libraries.

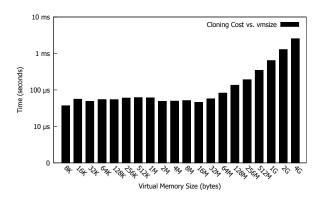

This work was published at SYSTOR in 2013 and is a direct result of my internship at Fusion-io. The paper argues that the current block layer within the Linux kernel is inadequate for current and future SSDs. We present the design of a new block layer, that allows the number of I/O per seconds available to scale with the number of cores in a system and with the device itself. Additionally, the engineering work reported in the paper led to significantly reduce the time spent by I/Os traversing the block layer. The work was integrated in the Linux kernel and upstreamed with Linux Kernel 3.13.

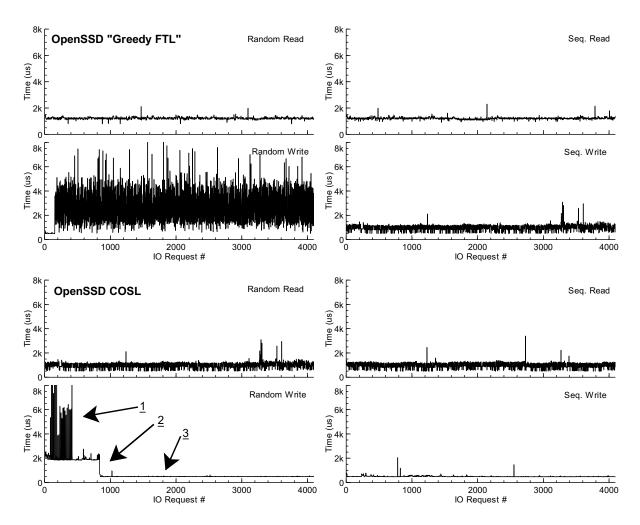

Step 3: In order to continue our endeavor, we needed to find new ways to explore the design space of cross layer optimizations involving operating system and SSDs. We considered simulation or custom-made hardware platforms. Both allow us to test our ideas. SSD simulators, such as DiskSim [1], FlashSim [3] and EagleTree [11], that Niv Dayan built as an extension of the simulator I built during my MSc thesis, allow us to prototype ideas quickly and understand their implications. Unfortunately, all the simulators are defined in user-space. None of them allow us prototype operating system kernel changes without significant latency overhead. Conversely, hardware platforms, such as OpenSSD [13, 16, 22] and Moneta [2], let us keep the code paths through the software stack without breaking compatibility, but requires significant plumping to yield a result. Moneta also assumes that applications access a SSD directly, without mediation from the operating system (an approach which is not a good match for our core thesis).

As a result, we decided to implement our own simulator, that performs I/O scheduling at run-time and allows users to directly measure the performance impact of any software and hardware design decision. The paper included in this thesis was presented at the Non-Volatile Memory Workshop (NVMW) in 2014.

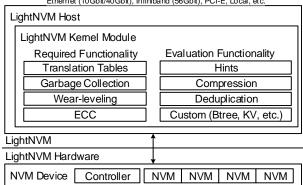

Step 4: Moving back to the original research question around the narrow block interface for SSDs, we extend the ideas that underlie the design of our simulator into an extension of the Linux block layer. A lot of interesting research towards cross-layer stack ideas have been proposed [10, 9] as well as extensions of block I/O interface [2, 18]. These approaches look at the overhead and guarantees of the OS, and moves parts or all OS logic into the SSD or the application. We take the dual approach. We wish to explore how far can we move SSD processing into the host software stack in order to improve performance.

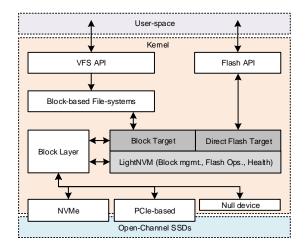

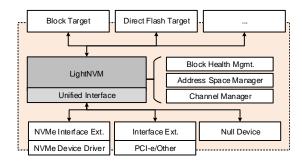

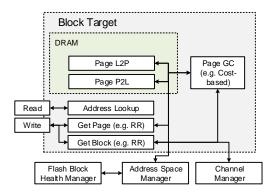

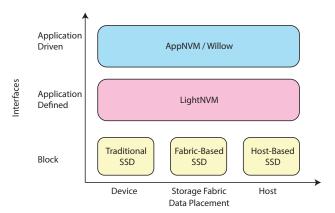

We extend the narrow block interface, with additional commands so that the SSD exposes its physical address space and flash commands directly to the host. We denote such SSDs, open-channel SSDs. Such SSDs were envisaged by Philippe Bonnet and Luc Bouganim back in 2011 [19]. At the time it was science fiction. Today, all major Internet service and public cloud providers rely on their own custom-made open channel SSDs. SSD controller vendors are competing to define products adapted for such SSDs. Memblaze already commercializes a version of its PBlaze3 SSD as open channel SSDs.

We defined the LightNVM specification<sup>1</sup>, that describes a command set to communicate the characteristics of SSDs, and allows the host to implement a generic layer, which can either be used to implement a host-side FTL, similarly to the Virtual Storage Layer provided by Fusion-io, or move FTLs (we call these targets) into the applications itself. Light-NVM allows applications to work together on the same address space, and thus maintain access to storage, without going though the kernel (if

<sup>&</sup>lt;sup>1</sup>LightNVM Specification Draft: http://goo.gl/BYTjLI

that is the wish), but still consult the kernel for chunk accesses (1-16MB). This provides a less granular split of accesses and thus allows the CPU overhead to scale with the speed of the storage device. Allowing applications to directly optimize their data placement on top of SSDs, removes the need for intermediate layers, such as file-systems. LightNVM<sup>2</sup> is currently being prepared for the Linux kernel and will soon hit upstream, with several SSD vendors implementing the command set to bringing application-defined storage to the next-generation storage systems. The paper included in this thesis will be submitted to FAST 2016.

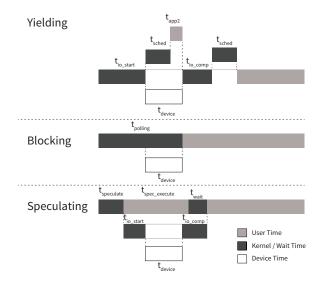

Step 5: Looking forward, we consider the problem of processing I/Os with future SSDs whose latency lies in the microsecond range with throughput of millions of I/Os per seconds. Our work was inspired by the FAST 2012 paper [4] introducing pull versus poll. For SSDs that whose latency lied in the 5-10us range, it was not very clear if a pull or poll model should be used. By introducing speculation into the mix, we enable applications to keep on working, without waiting for I/O completion. The paper included in this thesis is a collaboration with Michael Wei from UCSD. The paper was published at the Usenix Annual Technical Conference in 2014.

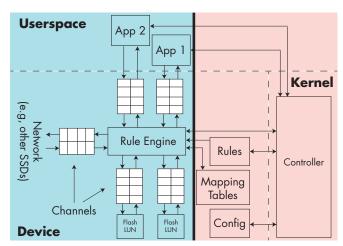

Step 6: For future high-performance SSDs, we looked at what kind of processing could be moved back to the SSD, and possibly encoded in hardware, in order to basically get the operating system out of the data path, with quality of service guarantees enforced on the control path. Today, performing fairness is fully disregarded for SSDs (CFQ and other I/O schedulers are very often disabled for SSDs). We argue that a

<sup>2</sup>Website: http://github.com/OpenChannelSSD

rule-based approach, which could be efficiently supported in hardware, would be a significant improvement of the state of the art. The position paper included in this thesis was presented at the Non-Volatile Memory Workshop in 2015 and constitutes the basis for a patent application.

In summary, this thesis has the following four major contributions:

- Questioning whether the narrow block interface is the right interface for the future (Paper 1, 6);

- Defining a new block layer within the Linux Kernel to add scalability for the storage stack in the Linux kernel (Paper 2);

- Defining a new software framework for controlling SSDs by moving data placement decisions into the host (Paper 4);

- At last, opportunities for enabling faster storage accesses and intelligent I/O processing on SSDs with microsecond latency (Paper 3, 5).

## 1.6 Structure of the Thesis

The thesis is structured around these 6 contributions. Paper 1 "Necessary Death of the Block Device Interface" [4] presented at CIDR 2013. Paper 2, together with Jens Axboe, "Linux Block IO: Introducting Multiqueue SSD Access on Multi-core Systems" [3] presented at SYSTOR 2013. Paper 3, together with Michael Wei from UCSD, "I/O Speculation for the Microsecond Era" [25] presented at USENIX ATC 2014. Paper 4, "LightNVM: Lightning Fast Evaluation Platform for Non-Volatile Memories" [1] presented at the Non-Volatile Memory Workshop. Paper 5,

"Open-Channel Solid State Drives" short paper presented at the Non-Volatile Memory Workshop and Linux Software Foundation Vault 2015. Long version to be submitted to FAST 2016. At last Paper 6, "AppNVM: A software-defined, application-driven SSD" [6] presented at the Non-Volatile Memory Workshop 2015. Finally, the manuscript offers concluding remarks, open issues and directions for future work.

# Literature

- [1] Nitin Agrawal, Vijayan Prabhakaran, Ted Wobber, J.D. Davis, Mark Manasse, and Rina Panigrahy. Design tradeoffs for SSD performance. In *USENIX 2008 Annual Technical Conference on Annual Technical Conference*, number June, pages 57–70. USENIX Association, 2008.

- [2] AC Arpaci-Dusseau and RH Arpaci-Dusseau. Removing the costs of indirection in flash-based SSDs with nameless writes. *HotStorage'10 Proceedings of the 2nd USENIX conference on Hot topics in storage and file systems*, 2010.

- [3] Matias Bjø rling, Jens Axboe, David Nellans, and Philippe Bonnet. Linux Block IO: Introducing Multi-queue SSD Access on Multi-core Systems. *Proceedings of the 6th International Systems and Storage Conference*, 2013.

- [4] Matias Bjø rling, Philippe Bonnet, Luc Bouganim, and Niv Dayan. The Necessary Death of the Block Device Interface. In *6th Biennial Conference on Innovative Data Systems Research (CIDR)*, 2013.

- [5] Matias Bjø rling, Jesper Madsen, Philippe Bonnet, Aviad Zuck, Zvonimir Bandic, and Qingbo Wang. LightNVM: Lightning Fast Evaluation Platform for Non-Volatile Memories. In Non-Volatile Memories Workshop, NVMWorkshop'14, 2014.

- [6] Matias Bjø rling, Michael Wei, Javier González, Jesper Madsen, and Philippe Bonnet. AppNVM: A software-defined, application-driven SSD. In *Non-Volatile Memories Workshop*, 2015.

- [7] John S Bucy, Jiri Schindler, Steven W Schlosser, and Gregory R

- Ganger. The DiskSim Simulation Environment. *Parallel Data Laboratory*, 2008.

- [8] Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollow, Rajesh K. Gupta, and Steven Swanson. Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-volatile Memories. 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture, pages 385–395, December 2010.

- [9] Adrian M. Caulfield, Todor I. Mollov, Louis Alex Eisner, Arup De, Joel Coburn, and Steven Swanson. Providing safe, user space access to fast, solid state disks. *Proceedings of the seventeenth international conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS)*, page 387, 2012.

- [10] Joel Coburn, Adrian M Caulfield, Laura M Grupp, Rajesh K Gupta, and Steven Swanson. NV-Heaps: Making Persistent Objects Fast and Safe with Next-Generation, Non-Volatile Memories. In ACM SIGARCH Computer Architecture News, 2011.

- [11] Niv Dayan, MK Svendsen, and Matias Bjø rling. EagleTree: exploring the design space of SSD-based algorithms. *Proceedings of the VLDB Endowment*, 2013.

- [12] Peter J Denning. ACM President's Letter: What is experimental computer science? *Communications of the ACM*, 23(10), 1980.

- [13] Amber Huffman. NVM Express Specification 1.1. 2012.

- [14] Kim Joohyun, Haesung Kim, Seongjin Lee, and Youjip Won. FTL Design for TRIM Command. *The Fifth International Workshop on Software Support for Portable Storage*, pages 7–12, 2010.

- [15] Youngjae Kim, Brendan Tauras, Aayush Gupta, and Bhuvan Urgaonkar. FlashSim: A Simulator for NAND Flash-Based Solid-State Drives. 2009 First International Conference on Advances in System Simulation, pages 125–131, September 2009.

- [16] Sang-won Lee and Jin-soo Kim. Understanding SSDs with the OpenSSD Platform. *Flash Memory Summit*, 2011.

- [17] Oracle Nesheim, Bill. Mythbusting Flash Performance. *Flash Memory Summit*, 2011.

- [18] Xiangyong Ouyang, David Nellans, Robert Wipfel, David Flynn, and D.K. Panda. Beyond block I/O: Rethinking traditional storage primitives. In *High Performance Computer Architecture (HPCA)*, 2011 *IEEE 17th International Symposium on*, pages 301–311. IEEE, 2011.

- [19] Luc Bouganim Philippe Bonnet. Flash Device Support for Database Management. 5th Biennial Conference on Innovative Data Systems Research (CIDR), 2011.

- [20] C. Ruemmler and J. Wilkes. An introduction to disk drive modeling. *IEEE Computer*, 27(3):17–28, March 1994.

- [21] Mohit Saxena, Yiying Zhang, Michael M Swift, Andrea Arpaci-Dusseau C, and Remzi H Arpaci-Dusseau. Getting Real: Lessons in Transitioning Research Simulations into Hardware Systems. In *Proceedings of the 11th USENIX conference on File and Storage Technologies (FAST)*, 2013.

- [22] Yong Ho Song, Sanghyuk Jung, Sang-won Lee, and Jin-soo Kim. Cosmos OpenSSD: A PCIe-based Open Source SSD Platform OpenSSD Introduction. *Flash Memory Summit*, pages 1–30, 2014.

- [23] Curtis E Stevens and Dan Colgrove. Technical Comittee TI13 ATA / ATAPI Command Set 2. 2010.

- [24] Dejan Vučinić, Qingbo Wang, Cyril Guyot, Robert Mateescu, Filip Blagojević, Luiz Franca-neto, Damien Le Moal, Hgst San, Trevor Bunker, Jian Xu, Steven Swanson, San Diego, Santa Clara, and Zvonimir Bandi. DC Express: Shortest Latency Protocol for Reading Phase Change Memory over PCI Express. 12th USENIX Conference on File and Storage Technologies (FAST), 2014.

- [25] Michael Wei, Matias Bjø rling, Philippe Bonnet, and Steven Swanson. I/O Speculation for the Microsecond Era. In *USENIX Annual Technical Conference*, 2014.

- [26] Jisoo Yang, DB Minturn, and Frank Hady. When poll is better than

interrupt. *Proceedings of the 10th USENIX conference on File and Storage Technologies (FAST)*, pages 1–7, 2012.

# Chapter 2

# The Necessary Death of the Block Device Interface

The premise of the CLyDE project is that the strict layering that has been so successful for designing database systems on top of magnetic disks is no longer applicable with SSDs based on existing observation that SSD performance varies a lot and in unpredictable ways [7, 8, 6, 9, 3, 14, 5, 12].

To start the thesis, I spent time reviewing the literature and surveying existing assumptions about SSD performance model. I found that most papers made a set of assumptions, most often implicitely about SSD performance. the original plan was to evaluate these assumptions experimentally. It turned out that an analysis based on a clear understanding of SSD internals was sufficient to show that SSD complexity was not captured by existing performance models. The first part of the following paper thus makes the case against the narrow block device interface.

But what then? If the block device interface is not appropriate, how should secondary storage be abstracted? And how would hardware evolution, in particular the advent of byte addressable persistent memory, impact such an abstraction? We propose a vision that addresses these questions in the second part of this paper.

This vision paper, called "The Necessary Death of the Block Device Interface", was published at CIDR in 2013.

After the paper was published, it has been discussed at workshops and presentations in the industry [1, 2]. Interfaces have been specifically designed to change the way the block device interface is used in large cloud data-centers [11], moving from a block device abstraction per SSD to a block device abstraction per flash chip in a SSD. Similarly, NVMKV [10], NVMFS [2, 13] propose special purpose instantiations of the storage block interface.

What was a slightly unconventional take on SSD performance characterisation has now become a mainstream view. For example, it was the view adopted by all indutrial presenters at the EMC University Flash Forum in September 2014. Note though that some industry players are still very much attached to the block device interface to keep the status quo and a very profitable business as long as possible. So the block device interface is not going to disappear any time soon. The point I make in the paper though is that it has become a legacy that should no longer constraint system research.

# Literature

- [1] EMC University Flash Forum, September. 2014.

- [2] Memblaze Flash Forum, May. 2015.

- [3] Aayush Gupta, Youngjae Kim, and Bhuvan Urgaonkar. DFTL: A Flash Translation Layer Employing Demand-based Selective Caching of Page-level Address Mappings. *ACM SIGPLAN Notices*, 44(3):229, February 2009.

- [4] William K. Josephson, Lars a. Bongo, Kai Li, and David Flynn. DFS: A File System for Virtualized Flash Storage. *ACM Transactions on Storage*, 6(3):1–25, September 2010.

- [5] Dawoon Jung, Jeong-UK Kang, Heeseung Jo, Jin-Soo Kim, and Joonwon Lee. Superblock FTL: A Superblock-Based Flash Translation Layer with a Hybrid Address Translation Scheme. *ACM Transactions on Embedded Computing Systems*, 9(4):1–41, March 2010.

- [6] J KANG, J KIM, C PARK, H PARK, and J LEE. A multi-channel architecture for high-performance NAND flash-based storage system. *Journal of Systems Architecture*, 53(9):644–658, September 2007.

- [7] Jesung Kim, Jong Min Kim, Sam H Noh, Sang Lyul Min, and Yookun Cho. A space-efficient flash translation layer for CompactFlash systems. *IEEE Transactions on Consumer Electronics*, 48(2):366–375, May 2002.

- [8] Sang-Won Lee, Dong-Joo Park, Tae-Sun Chung, Dong-Ho Lee,

- Sangwon Park, and Ha-Joo Song. FAST: A log buffer-based flash translation layer using fully-associative sector translation. *ACM Transactions on Embedded Computing Systems*, 6(3), July 2007.

- [9] Sungjin Lee, Dongkun Shin, Young-Jin Kim, and Jihong Kim. LAST: locality-aware sector translation for NAND flash memory-based storage systems. *ACM SIGOPS Operating Systems Review*, 42(6):36–42, October 2008.

- [10] Leonardo Mármol, Swaminathan Sundararaman, Nisha Talagala, Raju Rangaswami, Sushma Devendrappa, Bharath Ramsundar, and Sriram Ganesan. NVMKV: A Scalable and Lightweight Flash Aware Key-Value Store. 6th USENIX Workshop on Hot Topics in Storage and File Systems, 2014.

- [11] Jian Ouyang, Shiding Lin, S Jiang, and Z Hou. SDF: Software-defined flash for web-scale internet storage systems. In Proceedings of the 19th international conference on Architectural support for programming languages and operating systems, 2014.

- [12] Dongchul Park, Biplob Debnath, and David H.C. Du. A Workload-Aware Adaptive Hybrid Flash Translation Layer with an Efficient Caching Strategy. In 2011 IEEE 19th Annual International Symposium on Modelling, Analysis, and Simulation of Computer and Telecommunication Systems, pages 248–255. IEEE, July 2011.

- [13] Mohit Saxena, Yiying Zhang, Michael M Swift, Andrea Arpaci-Dusseau C, and Remzi H Arpaci-Dusseau. Getting Real: Lessons in Transitioning Research Simulations into Hardware Systems. In *Proceedings of the 11th USENIX conference on File and Storage Technologies (FAST)*, 2013.

- [14] Qingsong Wei, Bozhao Gong, Suraj Pathak, Bharadwaj Veeravalli, Lingfang Zeng, and Kanzo Okada. WAFTL: A Workload Adaptive Flash Translation Layer with Data Partition. Symposium on Massive Storage Systems and Technologies and Co-located Events, 2011.

# The Necessary Death of the Block Device Interface

Matias Bjørling<sup>1</sup>, Philippe Bonnet<sup>1</sup>, Luc Bouganim<sup>2,3</sup>, Niv Dayan<sup>1</sup>

<sup>1</sup> IT University of Copenhagen Copenhagen, Denmark {mabj,phbo,nday}@itu.dk <sup>2</sup> INRIA Paris-Rocquencourt Le Chesnay, France Luc.Bouganim@inria.fr <sup>3</sup> PRISM Laboratory Univ. of Versailles, France Luc.Bouganim@prism.uvsq.fr

#### **ABSTRACT**

Solid State Drives (SSDs) are replacing magnetic disks as secondary storage for database management as they offer orders of magnitude improvement in terms of bandwidth and latency. In terms of system design, the advent of SSDs raises considerable challenges. First, the storage chips, which are the basic component of a SSD, have widely different characteristics - e.g., copy-onwrite, erase-before-write and page-addressability for flash chips vs. in-place update and byte-addressability for PCM chips. Second, SSDs are no longer a bottleneck in terms of IO latency forcing streamlined execution throughout the I/O stack to minimize CPU overhead. Finally, SSDs provide a high degree of parallelism that must be leveraged to reach nominal bandwidth. This evolution puts database system researchers at a crossroad. The first option is to hang on to the current architecture where secondary storage is encapsulated behind a block device interface. This is the mainstream option both in industry and academia. This leaves the storage and OS communities with the responsibility to deal with the complexity introduced by SSDs in the hope that they will provide us with a robust, yet simple, performance model. In this paper, we show that this option amounts to building on quicksand. We illustrate our point by debunking some popular myths about flash devices and pointing out mistakes in the papers we have published throughout the years. The second option is to abandon the simple abstraction of the block device interface and reconsider how database storage manager, operating system drivers and SSD controllers interact. We give our vision of how modern database systems should interact with secondary storage. This approach requires a deep cross-layer understanding and a deep re-design of the database system architecture, which is the the only viable option for database system researchers to avoid becoming irrelevant.

#### 1. INTRODUCTION

For the last thirty years, database systems have relied on magnetic disks as secondary storage [18]. Today, the growing performance gap between processors and magnetic disk is pushing solid-state drives (SSDs) as replacements for disks [10]. SSDs are based on non-volatile memories such as flash and PCM (Phase-Change memory). They offer great performance at an ever-decreasing cost. Today, tens of flash chips wired in parallel behind a safe cache deliver hundreds of thousands accesses per second at a latency of tens of microseconds. Compared to modern hard disks, this is a hundredfold improvement in terms of bandwidth and latency, at ten-times the cost. New SSD technologies, such as PCM, promise to keep on improving performance at a fraction of the cost.

It has now been six years since Jim Gray pointed out the significance of flash-based SSDs. Has a new generation of database systems emerged to accommodate those profound changes? No. Is a new generation of database systems actually needed? Well, the jury is up. There are two schools of thoughts:

- The conservative approach, taken by all database constructors, and many in the research community, is to consider that the advent of SSDs does not require any significant re-design. The fact that SSDs offer the same block device interface as magnetic disks allows preserving existing database systems, running them unchanged on SSDs (slight adaptations being sold as SSD-optimizations). A fraction of radical conservatives ignore SSDs and keep on writing articles and grant proposals based on disks, as if we were in the 90s (How will they teach about database systems in five years, when none of their bachelor students has ever seen a disk?) More moderate conservatives, focusing on storage management, consider that database systems have to be redesigned on top of the block device interface, based on the new performance characteristics of SSDs. The hope is that the storage and operating system communities provide a robust, yet simple, performance model for the new generation of storage devices.

- The progressive approach is to consider that the advent of SSDs, and non-volatile memories more generally, requires a complete re-thinking of the interactions between database system, operating system and storage devices. The argument is that SSDs challenge the strict layering established between these components on the basis of a simple performance contract, e.g., sequential access is no longer orders of magnitude faster than random access, SSDs are no longer the bottleneck in terms of latency, SSDs require a high-level of parallelism, SSDs do not constitute a homogeneous class of devices (as opposed to disks). This approach, that requires a deep cross layer understanding, is mainstream in the operating system and storage research communities [7,9,13]; not yet in the database systems research community.

The premise of the conservative approach is that the block device interface should be conserved as a robust abstraction that allows the operating system to hide the complexity of I/O management without sacrificing performance. We show, in Section 2, that this assumption does not hold; neither for flash-based nor for PCM-based devices. Worse, we show that it leads to brittle research based on myths rather than sound results. We debunk a few of these myths, illustrating our points with mistakes published in the articles we have written throughout the years.

In Section 3, we present the challenges that SSDs and non-volatile memories raise in terms of system design and discuss how they impact database systems. We present our vision of the necessary collaboration between database storage manager and operating system.

Note that we do not dispute that the conservative approach is economically smart. Neither do we ignore the fact that disks still largely dominate the storage market or that the block device interface will live on as a legacy for years. Our point is that the advent of SSDs and non-volatile memories has a deep impact on

system design, and that we, as database systems researchers, must re-visit some grand old design decisions and engage with the operating system and storage communities in order to remain relevant.

# 2. THE CASE AGAINST BLOCK DEVICES

#### 2.1 SSD MYTHS

Even if the block device interface has been challenged for some years [17], these critics have had, so far, a limited impact. For instance, all research papers published in the database community, proposing new storage models, indexing methods or query execution strategies for flash devices still build on the premise of SSDs encapsulated behind a block device interface [5]. All of these approaches assume, more or less explicitly, a simple performance model for the underlying SSDs. The most popular assumptions are the following:

- SSDs behave as to the non-volatile memory they contain:

Before flash-based SSDs became widely available, there was

a significant confusion between flash memory and flash

devices. Today, we see a similar confusion with PCM.

- On flash-based SSDs random writes are extremely costly, and should be avoided: This was actually always true for flash devices on the market before 2009. Moreover, this rule makes sense after a quick look at flash constraints and SSD architecture. Many thus propose to avoid random writes using buffering and log-based strategies

- On flash-based SSDs, reads are cheaper than writes: Again this seems to make sense because, (1) reads on flash chips are much cheaper than writes (the so-called program operations);

(2) flash chip constraints impact write operations (need for copy-on-write as in-place updates are forbidden on a flash chip);

(3) flash devices have no mechanical parts. Some proposals are built on this rule, making aggressive use of random read IOs.

We will show in Section 2.3 that these assumptions about (flash-based) SSDs are plain wrong, but first, let us review the internals of a flash-based IO stack -- from flash chips to the OS block layer.

#### 2.2 I/O STACK INTERNALS

A point that we would like to carry across is that we, as database researchers, can no longer consider storage devices as black boxes that respect a simple performance contract. We have to dig into their internals in order to understand the impact of these devices on system design. Here is a bottom up review of the IO stack with flash-based SSDs. We discuss PCM in Section 2.4.

Flash chip: A flash chip is a complex assembly of a huge number of flash cells<sup>1</sup>, organized by pages (512 to 4096 bytes per page), blocks (64 to 256 pages per block) and sometimes arranged in multiple *planes* (typically to allow parallelism across planes). Operations on flash chips are read, write (or program) and erase. Due to flash cells characteristics, these operations must respect the following constraints: (C1) reads and writes are performed at the granularity of a page; (C2) a block must be erased before any of the pages it contains can be overwritten; (C3) writes must be sequential within a block; (C4) flash chips support a limited number of erase cycles. The trends for flash memory is towards an increase (i) in density thanks to a smaller process (today 20nm), (ii) in the number of bits per flash cells, (iii) of page and block

<sup>1</sup> See [5] for a discussion of flash cells internals.

size, and (iv) in the number of planes. Increased density also incurs reduced cell lifetime (5000 cycles for triple-level-cell flash), and raw performance decreases. For now, this lower performance can be compensated by increased parallelism within and across chips. At some point though, it will be impossible to further reduce the size of a flash cell. At that point, PCM might be able to take over and still provide exponential growth in terms of density.

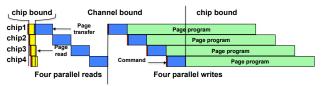

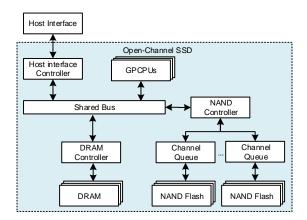

Flash SSD: A flash-based SSD contains tens of flash chips wired in parallel to the SSD controller though multiple channels. Flash chips are decomposed into logical units (LUN). LUNs are the unit of operation interleaving, i.e., operations on distinct LUNs can be executed in parallel, while operations on a same LUN are executed serially. We consider that SSD performance is *channel-bound* if channels are the bottleneck and IOs wait for a channel to be available before they can be executed. SSD performance is *chip-bound* if chip operations are the bottleneck and IOs wait for a chip operation to terminate before they can be executed. Figure 1 illustrates these notions on an example.

Figure 1: Example of channel transfer and chip operations on four chips (we assume 1 LUN per chip) attached to the same channel.

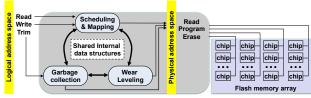

**SSD controller:** The SSD controller embeds the so-called Flash Translation Layer (FTL) that maps incoming application IOs –a read, a write or a trim<sup>2</sup> on a logical block address (LBA)– into appropriate chip operations. As illustrated on Figure 2, FTL is responsible for:

- Scheduling & Mapping: The FTL provides a virtualization of

the physical address space into a logical address space. This

mapping is done at the page (and possibly block) level. The

FTL implements out-of-place updates (copy-on-write) to

handle C2 and C3. It also handles chip errors and deals with

parallelism across flash chips. While each read (resp. trim)

operation is mapped onto a specific chip, each write operation

can be scheduled on an appropriate chip.

- Garbage Collection: Each update leaves an obsolete flash page (that contains the before image). Over time such obsolete flash pages accumulate, and must be reclaimed through garbage collection.

- Wear Leveling: The FTL relies on wear-leveling to address C4--distributing the erase counts across flash blocks and masking bad blocks.

Figure 2: Internal architecture of a SSD controller

24

<sup>&</sup>lt;sup>2</sup> The Trim command has been introduced in the ATA interface standard to communicate to a flash device that a range of LBAs are no longer used by an application

Note that both the garbage collection and wear leveling modules read live pages from a victim block and write those pages (at a location picked by the scheduler), before the block is erased. The garbage collection and wear leveling operations thus interfere with the IOs submitted by the applications.

OS Driver: SSDs are not directly accessible from the CPU; the operating system provides a driver that manages communications to and from the device. Most SSDs implement a SATA interface and are accessed via the generic SATA driver. Some high-end SSDs (e.g., ioDrive from FusionIO) are directly plugged on the PCI bus. They provide a specific driver, which implements part of the SSD controller functionalities (leveraging CPU and RAM on the server to implement part of the FTL).

**Block Layer**: The block layer provides a simple memory abstraction. It exposes a flat address space, quantized in logical blocks of fixed size, on which I/O (read and write) requests are submitted. I/O requests are asynchronous. When an I/O request is submitted, it is associated to a completion queue. A worker thread then sends a page request to the disk scheduler. When the page request completes, an interrupt is raised (within the device driver), and the I/O request completes. In the last few years, the Linux block layer has been upgraded to accommodate SSDs and multicores. CPU overhead has been reduced—it was acceptable on disk to reduce seeks—, lock contention has been reduced, completions are dispatched on the core that submitted the request, and currently, the management of multiple IO queues for each device is under implementation.

Is it still reasonable to hide all this complexity behind a simple memory abstraction? Let us now revisit the performance assumptions popular in the database community.

#### 2.3 DEBUNKING SSD MYTHS

(1) SSDs behave as to the non-volatile memory they contain.

Hopefully, the previous section will have made it very clear that this statement is not true. We pointed out this confusion in [6]. Still, two years later, we proposed a bimodal FTL that exposed to applications the constraints of a single flash chip [4]. We ignored the intrinsic parallelism of SSDs and the necessary error management that should take place within a device controller. Exposing flash chip constraints through the block layer, as we proposed, would in effect suppress the virtualization of the physical flash storage. This would limit the controller's ability to perform garbage collection and wear leveling (as it could not redirect the live pages of a victim block onto other chips) and its ability to deal with partial chip failures. It would also put a huge burden on the OS block layer if the application aimed at efficiently leveraging SSD parallelism by scheduling writes on multiple chips. Today, papers are published that attribute the characteristics of a phase-change memory chip to a SSD, thus ignoring that parallelism and error management must be managed at the SSD level.

# (2) On flash-based SSDs, random writes are very costly and should be avoided.

While this statement was true on early flash-based SSDs, it is no longer the case [2,3,5]. There are essentially two reasons why a flash-based SSD might provide random writes which are as fast as, or even faster than sequential writes. First, high-end SSDs now include safe RAM buffers (with batteries), which are designed for buffering write operations. Such SSDs provide a form of write-back mechanism where a write I/O request completes as soon as it hits the cache. Second, modern SSD can rely on page mapping, either because mapping is stored in the driver (without much

RAM constraints), or because the controller supports some form of efficient page mapping cache (e.g., DFTL [10]). With page mapping, there are no constraints on the placement of any write – regardless of whether they are sequential or random. Thus a controller can fully benefit from SSD parallelism when flushing the buffer regardless of the write pattern! An interesting note is that random writes have a negative impact on garbage collection, as locality is impossible to detect for the FTL. As a result, pages that are to be reclaimed together tend to be spread over many blocks (as opposed to sequential writes where locality is easy to detect). Quantifying these effects is a topic for future work. To sum up, the difference between random writes and sequential writes on flash-based SSDs is rather indirect. We completely missed that point in [4], where we ventured design hints for SSD-based system design.

#### (3) On flash-based SSDs, reads are cheaper than writes.

While at the chip level reads are much faster than writes, at the SSD level this statement is not necessarily true. First, for reads, any latency or delay in the execution leads to visible latency in the application. It is not possible to hide this latency behind a safe cache, as it is the case for writes. So if subsequent reads are directed to a same LUN and, if that LUN or the associated channel is busy, then the read operation must wait (e.g., wait 3ms for the completion of an erase operation on that LUN)! Third, reads will benefit from parallelism only if the corresponding writes have been directed to different LUNs (on different channels). As we have seen above, there is no guarantee for this. Fourth, reads tend to be channel-bound --while writes tend to be chip-bound --, and channel parallelism is much more limited than chip parallelism.

#### 2.4 DISCUSSION

It is unlikely that the complexity of flash-based SSDs can be tamed into a simple performance model behind the block device interface. So what should we do? An option is to wait for the OS and storage communities to define such a model. In the meantime, we should stop publishing articles based on incorrect assumptions. Another option is to skip the complexity of flash-based SSDs and wait for PCM to take over, as the characteristics of PCM promise to significantly reduce complexity (in-place updates, no erases, on-chip error detection, no need for garbage collection). First, there is a large consensus that PCM chips should be directly plugged onto the memory bus (because PCM is byte addressable and exhibits low latency) [7,15]. The capacity of each PCM chip is unlikely to be much larger than RAM chips. That still leaves us with the problem of secondary storage. Second, PCM is likely to be integrated into flash-based SSDs, i.e., to expand buffer capacity and performance. As a result, flash-based SSDs are unlikely to disappear any time soon. Third, even if we contemplate pure PCM-based SSDs [1], the issues of parallelism, wear leveling and error management will likely introduce significant complexity. Also, PCM-based SSDs will not make the issues of low latency and high-parallelism disappear. More generally. PCM and flash mark a significant evolution of the nature of the interactions between CPU, memory (volatile as well as non-volatile) and secondary storage. This is an excellent opportunity to revisit how database systems interact with secondary storage.

#### 3. SECONDARY STORAGE REVISITED

For years, we have assumed that persistence was to be achieved through secondary storage, via a memory abstraction embodied by the block device interface. The advent of SSDs force us to reconsider this assumption:

- We can now achieve persistence through PCM-based SSDs plugged on the memory bus and directly addressable by the CPU [6], in addition to secondary storage, composed of flash-based SSDs.

- 2. Flash-based SSDs are no longer accessed via a strict memory abstraction. The TRIM command has been added to read and write to make it possible to applications to communicate to a SSD that a range of logical addresses were no longer used and could thus be un-mapped by the FTL. SSD constructors are now proposing to expose new commands, e.g., atomic writes [17], at the driver's interface. More radically, FusionIO is now proposing direct access to its driver, entirely bypassing the block layer (ioMemory SDK). The point here is that the block device interface provides too much abstraction in the absence of a simple performance model.

This evolution forces us to re-visit the nature of persistence in database systems. We see three fundamental principles:

- We should keep synchronous and asynchronous patterns separated, as Mohan suggested [16]. Until now, database storage managers have implemented conservative asynchronous I/O submission policies to account for occasional synchronous I/Os [13]. Instead synchronous patterns (log writes, buffer steals under memory pressure) should be directed to PCM-based SSDs via non-volatile memory accesses from the CPU, while asynchronous patterns (lazy writes, prefetching, reads) should be directed to flash-based SSDs via I/O requests.

- We should abandon the memory abstraction in favor of a communication abstraction to manage secondary storage, as we suggested in [4]. The consequence is that (a) the database system is no longer the master and secondary storage a slave (they are communicating peers), and (b) the granularity of interactions is not limited to blocks. This has far reaching consequences on space allocation and naming (extent-based allocation is irrelevant, nameless writes are interesting), the management of log-structured files (which is today handled both at the database level and within the FTL), the management of interferences between I/Os, garbage collection and wear leveling. Interestingly, Jim Gray noted in [11] that RAM locality is king. An extended secondary storage interface would allow us to efficiently manage locality throughout the I/O stack.

- We should seek inspiration in the low-latency networking literature. Secondary storage is no longer a bottleneck in terms of latency, and it requires parallelism to reach nominal bandwidth. A similar evolution has been witnessed for some years in the networking community, where the developments of network cards, and the advent of 10/40/100 GB Ethernet, forced them to tackle the problems caused by low-latency. The solutions they explored including cross-layer design, shared memory, use of FPGA, out-of-band signaling are very much relevant in the context of a re-designed I/O stack, all the way to a database system. Major differences include the need to manage state for I/O completion and the need to handle small requests.

Note that any evolution of the role of secondary storage will take place in the context of multi-core CPUs. So, the staging architecture [12], based on the assumption that all data is in-memory, should be the starting point for our reflection.

Why don't we let the OS community redefine the IO stack? Well, they are not waiting for us. Proposals are flourishing for PCM- based [9,7], flash-based [14] and even database storage [15] systems. Note that these approaches are based on actual storage hardware and complete system design. We argue that it is time for database system researchers to engage other systems communities to contribute to the on-going re-design of the I/O stack and rethink the role of persistence in database systems.

#### 4. CONCLUSION

In this paper, we established that the database systems research community has a flash problem. We argued that the high-level of abstraction provided by the block device interface is a significant part of the problem. We joined the choir of those who preach a redesign of the architecture of (single-site) database systems. We argued that we ignore the evolution of secondary storage at our own peril. First, because some of the assumptions we are making are myths rather than sound results. Second, because the on-going re-design of the I/O stack is an opportunity for intriguing research.

#### 5. REFERENCES

- A. Akel, A. Caulfield, T.Mollov, R.Gupta, S. Swanson. Onyx: A Prototype Phase Change Memory Storage Array. HotStorage 2011.

- [2] M. Bjørling, P. Bonnet, L. Bouganim, and B. T. Jönsson. Understanding the energy consumption of flash devices with uFLIP. IEEE Data Eng. Bull., December, 2010.

- [3] M. Bjørling, L. L. Folgoc, A. Mseddi, P. Bonnet, L. Bouganim, and B. Jonsson. Performing sound flash device measurements: some lessons from uFLIP. SIGMOD Conference, 2010.

- [4] P. Bonnet and L. Bouganim. Flash Device Support for Database Management. CIDR, 2011.

- [5] P. Bonnet, L. Bouganim, I. Koltsidas, S. Viglas. System Co-Design and Data Management for Flash Devices. VLDB 2011.

- [6] L. Bouganim, B. T. Jonsson, and P. Bonnet. uFLIP: Understanding flash I/O patterns. CIDR, 2009.

- [7] A. Caulfield, T. Mollov, L. Eisner, A. De, J. Coburn, S. Swanson: Providing safe, user space access to fast, solid state disks. ASPLOS 2012.

- [8] S. Chen, P. Gibbons, S. Nath: Rethinking Database Algorithms for Phase Change Memory. CIDR 2011.

- [9] J. Condit, E. B. Nightingale, C. Frost, E. Ipek, B. C. Lee, D. Burger, D. Coetzee: Better I/O through byte-addressable, persistent memory. SOSP 2009.

- [10] A. Gupta, Y. Kim, and B. Urgaonkar. DFTL: a flash translation layer employing demand-based selective caching of page-level address mappings. In ASPLOS, 2009.

- [11] J. Gray. Tape is dead, disk is tape, flash is disk, RAM locality is king. Pres. at the CIDR Gong Show, Asilomar, CA, USA, 2007.

- [12] Stavros Harizopoulos, Anastassia Ailamaki: A Case for Staged Database Systems. CIDR 2003

- [13] Christoffer Hall, Philippe Bonnet: Getting Priorities Straight: Improving Linux Support for Database I/O. VLDB 2005.

- [14] H. Lim, B. Fan, D. Andersen, M. Kaminsky: SILT: a memoryefficient, high-performance key-value store. SOSP 2011:1-13

- [15] M. Mammarella, S. Hovsepian, E. Kohler: Modular data storage with Anvil. SOSP 2009:147-160

- [16] C.Mohan, S.Bhattacharya. Implications of Storage Class Memories on Software Architectures. HPCA Workshop on the Use of Emerging Storage and Memory Technologies. 2010

- [17] X. Ouyang, D. W. Nellans, R. Wipfel, D. Flynn, D. K. Panda: Beyond block I/O: Rethinking traditional storage primitives. HPCA 2011.

- [18] S. W. Schlosser and G. R. Ganger. MEMS-based Storage Devices and Standard Disk Interfaces: A Square Peg in a Round Hole? USENIX FAST, 2004.

- [19] M. Stonebraker. Operating system support for database management. Commun. ACM, 24(7):412–418, 1981.

# Chapter 3

# Linux Block IO: Introducing Multi-queue SSD Access on Multi-core Systems

In the previous paper, we made the case agains the block device interface. The following paper proposes a new design for the Linux block layer. How is that consistent? Should we get rid of the block layer or should we improve it? There is a subtle difference between the block device interface (which defines the logical address space and read/write operations on secondary storage), and the operating system block layer, which is responsible for IO submission and completion. In principle, the block layer can support any form of storage abstraction. The focus of this paper is thus on adapting IO handling to modern SSDs and multi-core hosts (regardless of how secondary storage is actually abstracted).

For decades IO handling has been optimized for traditional harddrives. The software stack was specifically optimized for spinning harddrives, i.e. large block I/Os and sequential accesses. When SSDs were introduced the read and write block interface typical of traditional hard-drives was preserved. This design decision guaranteed adoption, but quickly revealed significant bottlenecks in the storage stack.

In response, applications incorporate lighter and faster data structures and algorithms [3, 1, 4] and particular NoSQL databases, such as MongoDB, LevelDB, Aerospike, etc. takes advantage of the new storage media. Applications specifically optimized for SSDs rapidly revealed that the operating system was the bottleneck and that it had to be improved in order to increase application performance.

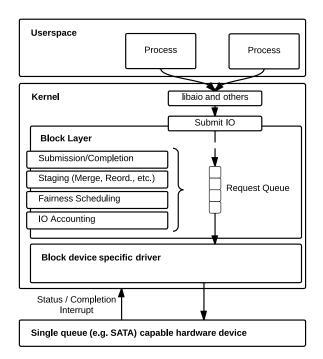

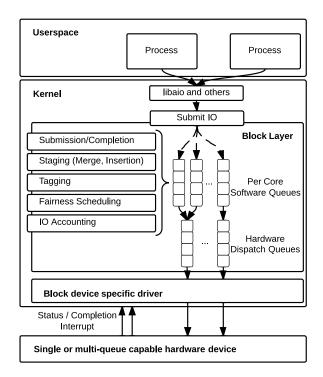

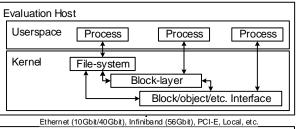

The kernel storage stack is composed by four core layers. From top to bottom: (i) I/Os arrive through system calls with a file descriptor (pread/pwrite, ioctl, libaio, etc.). On submission, (ii) the I/O is submitted to the file-system. The file-system maps the file I/O to its logical device sector and issue it to the appropriate storage device through the (iii) block layer. The block layer provides opportunity for merging I/Os, plugging, fairness between processes, etc. and at last issues one or multiple requests to a device driver. Finally, (iv) The device driver transforms the request to the corresponding hardware commands and issues it to the hardware device. The device completes the I/O and the host then complete the I/O back up through the storage stack layers.

Bottlenecks occurs in all of these layers in one way or another. We specifically target the block layer, as data-intensive applications often uses little of file-system features and thus expose bottlenecks in the block layer and device drivers. The block layer has traditionally optimized for hard-drives and its design choices actively prevents utilization of high

performance SSDs.

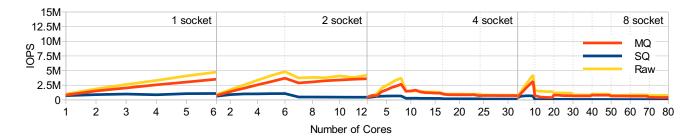

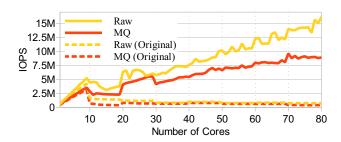

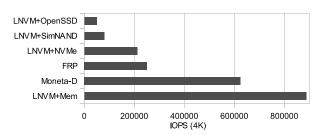

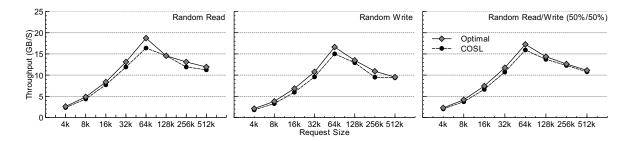

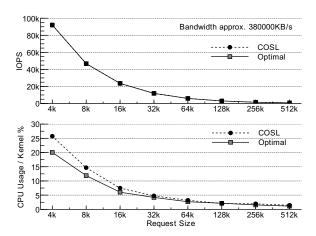

Our contribution is a scalable block layer for high-performance SSDs. The work is desbrived in "Linux Block IO: Introducing Multi-queue SSD Access on Multi-core Systems". It was presented at the SYSTOR 2013 conference. The contribution had three insights:

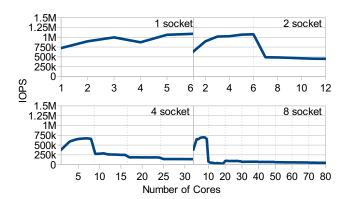

- The Linux kernel block layer is inadequate for high-performance SSDs. Benchmarking the block layer and heavily optimize for throughput showsthat the block layer is incapable to process more than 800-1000K IOPS.

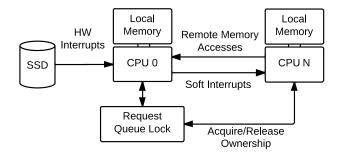

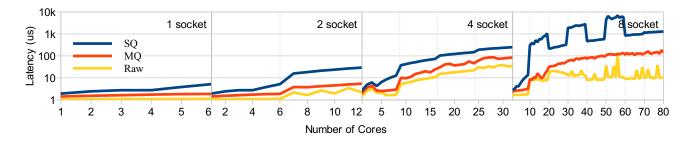

- SSDs that are capable of hundreds of thousands of IOPS, quickly overflow the attached CPU with interrupts. At high interrupt rates, a single CPU unit is dedicated to process I/O for other CPUs in the system. This increases latency, work and overhead for the complete system. To mitegate this, the new block layer allows I/Os to be routed using IRQ steering. IRQ steering enables the I/O system to send completion interrupt to the CPU that issued the I/O request, without interrupting the CPU of which the SSD is attached to.

- A core design of the original block layer is its single queue design. For each hard-drive in the system, there is a request queue allocated. Every time this queue is manipulated, its locks must be acquired and released. For each request, this can be multiple times. As merged, reordering and similar operatings are performed before its sent to the hard-drive for execution. This performs adequate on single CPU systems, but significantly exacerbated in multi-core and multi-nodes systems, preventing a scalable I/O stack.

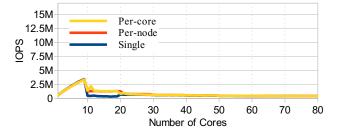

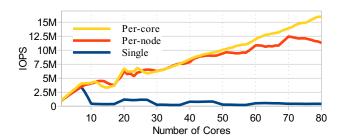

These three insights underlie the design of the multi-queue block layer (blk-mq). The new block layer introduces two sets of queues. A set of per-core queues and another set of hardware dispatch queues. The per-core queues are used for I/O merging, reordering, etc. of incoming I/O on a specific core. Eliminating any need for coordination with other queues in the set. The hardware dispatch queues matches the corresponding hardware capabilities. For example the AHCI standard for hard-drives supports a queue depth of 32 outstanding I/Os. A hardware dispatch queue is initialized with the same depth. When I/Os are submitted to the device driver, they are first added to the hardware dispatch queue and then submitted to the device driver one at a time. If the hardware has enough hardware queues to support all cores in a system. The submission of I/Os are performed directly on a single core without any synchronization across cores. The two queue set allows I/Os to be manipulated efficiently in a per-core data structures, and later when I/Os are pushed to the device driver, and not manipulated again, they are moved to the hardware dispatch queue for a specific hardware queue.

Note that, at the time the paper was published, there was no commercial SSD equipped with several hardware queues. The open channel SSDs that we discuss in Chapter 6 do provide several hardware queues. In fact all commercial SSDs based on NVMe now provide several hardware queues.

The new block layer scales from 800-1000K to 15M IOPS performing 512 bytes I/Os. Additionally, latency timings means are reduced both for low and high contension workloads. The best case reported in an 8-node setup. The latency was improved from 7.8x at full CPU utilization and

36x with half CPU utilization.

After the paper was published, blk-mq was accepted upstream in Linux kernel version 3.13. It has been improved significantly since its introduction with for example Scalable per-request data structures<sup>1</sup>, additional removal of locks in the hot path<sup>2</sup>, prototyping of polling [4]<sup>3</sup>, and converting significant amount of device drivers to blk-mq, including Micron mtip driver<sup>4</sup>, Intel NVMe driver<sup>5</sup>, ATA/SCSI stack<sup>6</sup>, device mapper<sup>7</sup>, virtio [2], and several others.

<sup>&</sup>lt;sup>1</sup>https://lkml.org/lkml/2014/6/2/329

<sup>&</sup>lt;sup>2</sup>https://lkml.org/lkml/2015/5/14/713

<sup>&</sup>lt;sup>3</sup>https://lkml.org/lkml/2013/6/20/591

<sup>&</sup>lt;sup>4</sup>https://lkml.org/lkml/2014/6/2/575

$<sup>^{5}</sup> http://lists.infradead.org/pipermail/linux-nvme/2014-October/001187.html \\$

<sup>&</sup>lt;sup>6</sup>http://lwn.net/Articles/602159/

<sup>&</sup>lt;sup>7</sup>https://www.redhat.com/archives/dm-devel/2015-March/msg00066.html

# Literature

- [1] Sang-Won Lee, Bongki Moon, Chanik Park, Jae-Myung Kim, and Sang-Woo Kim. A case for flash memory ssd in enterprise database applications. *Proceedings of the 2008 ACM SIGMOD international conference on Management of data SIGMOD '08*, page 1075, 2008.

- [2] Ming Lei. Virtio-blk Multi-queue Conversion and QEMU Optimization KVM Forum 2014 Virtio-blk Linux driver evolution. 2014.

- [3] Patrick O Neil, Edward Cheng, Dieter Gawlick, and Elizabeth O Neil. The log-structured merge-tree (LSM-tree). *Acta Informatica*, 33(4):1–32, 1996.

- [4] Dimitris Tsirogiannis and Stavros Harizopoulos. Query Processing Techniques for Solid State Drives Categories and Subject Descriptors. In *Proceedings of the 2009 ACM SIGMOD International Conference on Management of data*, 2009.

- [5] Jisoo Yang, DB Minturn, and Frank Hady. When poll is better than interrupt. *Proceedings of the 10th USENIX conference on File and Storage Technologies (FAST)*, pages 1–7, 2012.

# Linux Block IO: Introducing Multi-queue SSD Access on Multi-core Systems

Matias Bjørling\*†

Jens Axboet

\*IT University of Copenhagen {mabj,phbo}@itu.dk

# †Fusion-io {jaxboe,dnellans}@fusionio.com

David Nellans<sup>†</sup>

#### 785000 0 800k 0 600k 0 498000 498000 498000 498000 498000 58D1 58D2 58D3 58D4 58D5 2010 2011 2013

Philippe Bonnet\*

Figure 1: IOPS for 4K random read for five SSD devices.

#### **ABSTRACT**

The IO performance of storage devices has accelerated from hundreds of IOPS five years ago, to hundreds of thousands of IOPS today, and tens of millions of IOPS projected in five years. This sharp evolution is primarily due to the introduction of NAND-flash devices and their data parallel design. In this work, we demonstrate that the block layer within the operating system, originally designed to handle thousands of IOPS, has become a bottleneck to overall storage system performance, specially on the high NUMA-factor processors systems that are becoming commonplace. We describe the design of a next generation block layer that is capable of handling tens of millions of IOPS on a multi-core system equipped with a single storage device. Our experiments show that our design scales graciously with the number of cores, even on NUMA systems with multiple sockets.

#### **Categories and Subject Descriptors**

D.4.2 [Operating System]: Storage Management—Secondary storage; D.4.8 [Operating System]: Performance—measurements

#### **General Terms**

Design, Experimentation, Measurement, Performance.

#### **Keywords**

Linux, Block Layer, Solid State Drives, Non-volatile Memory, Latency, Throughput.

#### 1 Introduction

As long as secondary storage has been synonymous with hard disk drives (HDD), IO latency and throughput have been shaped by the physical characteristics of rotational devices: Random accesses that require disk head movement are slow and sequential accesses that only require rotation of the disk platter are fast. Generations of IO intensive algorithms and systems have been designed based on these two fundamental characteristics. Today, the advent of solid state disks (SSD) based on non-volatile memories (NVM)

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Permissions@acm.org.

SYSTOR '13, June 30 - July 02 2013, Haifa, Israel

Copyright is held by the owner/author(s). Publication rights licensed to ACM. Copyright 2013 ACM 978-1-4503-2116-7/13/06 ...\$15.00.

(e.g., flash or phase-change memory [11, 6]) is transforming the performance characteristics of secondary storage. SSDs often exhibit little latency difference between sequential and random IOs [16]. IO latency for SSDs is in the order of tens of microseconds as opposed to tens of milliseconds for HDDs. Large internal data parallelism in SSDs disks enables many concurrent IO operations which, in turn, allows single devices to achieve close to a million IOs per second (IOPS) for random accesses, as opposed to just hundreds on traditional magnetic hard drives. In Figure 1, we illustrate the evolution of SSD performance over the last couple of years.

A similar, albeit slower, performance transformation has already been witnessed for network systems. Ethernet speed evolved steadily from 10 Mb/s in the early 1990s to 100 Gb/s in 2010. Such a regular evolution over a 20 years period has allowed for a smooth transition between lab prototypes and mainstream deployments over time. For storage, the rate of change is much faster. We have seen a 10,000x improvement over just a few years. The throughput of modern storage devices is now often limited by their hardware (i.e., SATA/SAS or PCI-E) and software interfaces [28, 26]. Such rapid leaps in hardware performance have exposed previously unnoticed bottlenecks at the software level, both in the operating system and application layers. Today, with Linux, a single CPU core can sustain an IO submission rate of around 800thousand IOPS. Regardless of how many cores are used to submit IOs, the operating system block layer can not scale up to over one million IOPS. This may be fast enough for today's SSDs - but not for tomorrow's.